Non−Volatile RAM (NVRAM), PCMCIA Flash, and WIC.

Input/Output (I/O) Buses allow the M68360 to individually control other devices through the

SCCs. These include Universal Asynchronous Receiver/Transmitter (UART), the Ethernet

controller, and the WAN port interface.

♦

UART is an SCC integrated on the M68360. It provides the necessary user interface. It has one

RS232 port, and a data communications equipment (DCE) (console) RJ45. Note: UART has no

Auxiliary (data terminal equipment − DTE) port. Higher console speeds (upto 115.2 Kbps) are

supported. The downloading of Cisco IOS software images over the console port is supported using

xmodem or ymodem.

•

WAN interface cards (WICs) are media−specific network interfaces responsible for data transfer in

and out of the 160x series router. WICs communicate with the CPU through the CPU Bus for packet

transfer. Specialized Controllers (or application−specific integrated circuits − ASICs) used for media

support perform the above−mentioned functionality. WICs do not support Online Insertion and

Removal (OIR).

•

Power supply provides power to various components of the router.•

Memory Details

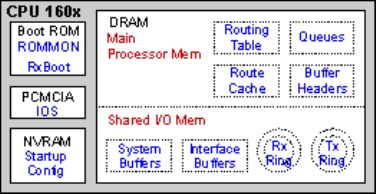

Different kinds of memory reside in the Cisco 1600 Series router, and each of them is handled in a different

way and for different purposes.

DRAM is logically divided in Main Processor memory and Shared Input/Output (I/O) memory.

Main Processor memory is used to store routing tables, fast switching cache, running configuration,

and so on. It can take unused shared I/O memory, if needed.

•

Shared I/O memory is used for temporary storage of packets in system buffers during process

switching, and interface buffers during fast switching. Cisco 1600 series routers running Cisco IOS

software versions prior to the integration of CSCdk40685 have a fixed I/O memory of 512 KB. (To

see details about this bug, go to the Bug Toolkit and type in CSCdk40685). After CSCdk40685, if the

router has enough memory, it allocates 25% to I/O memory. If not, I/O memory remains at 512 KB.

•

The way DRAM memory is distributed can be seen using the show memory summary command:

Router−1600#show memory summary

Head Total(b) Used(b) Free(b) Lowest(b) Largest(b)

Processor 20B3A7C 13419908 2334632 11085276 10907924 10907920

I/O 2D80000 4718592 247324 4471268 4466128 4464852

Physically, DRAM is a combination of 2 MB on−board non−parity chips, and one Single In−line Memory

Cisco 1600 Series Router Architecture