DM9161B

10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver

Final 14

Version: DM9161B-12-DS-F01

January 31, 2008

MII Interface (continued)

• TXER (transmit coding error) transitions are

synchronously with respect to TXCLK. If TXER is

asserted for one or more clock periods, and TXEN is

asserted, the PHY will emit one or more symbols that

are not part of the valid data delimiter set somewhere in

the frame being transmitted.

• RXD (receive data) is a nibble (4 bits) of data that are

sampled by the reconciliation sub layer synchronously

with respect to RXCLK. For each RXCLK period which

RXDV is asserted, RXD (3:0) are transferred from the

PHY to the MAC reconciliation sub layer.

• RXCLK (receive clock) output to the MAC reconciliation

sub layer is a continuous clock that provides the timing

reference for the transfer of the RXDV, RXD, and

RXER signals.

• RXDV (receive data valid) input from the PHY indicates

that the PHY is presenting recovered and decoded

nibbles to the MAC reconciliation sub layer. To interpret

a receive frame correctly by the reconciliation sub layer,

RXDV must encompass the frame, starting no later

than the Start-of-Frame delimiter and excluding any

End-Stream delimiter.

• RXER (receive error) transitions are synchronously with

respect to RXCLK. RXER will be asserted for 1 or more

clock periods to indicate to the reconciliation sub layer

that an error was detected somewhere in the frame

being transmitted from the PHY to the reconciliation sub

layer.

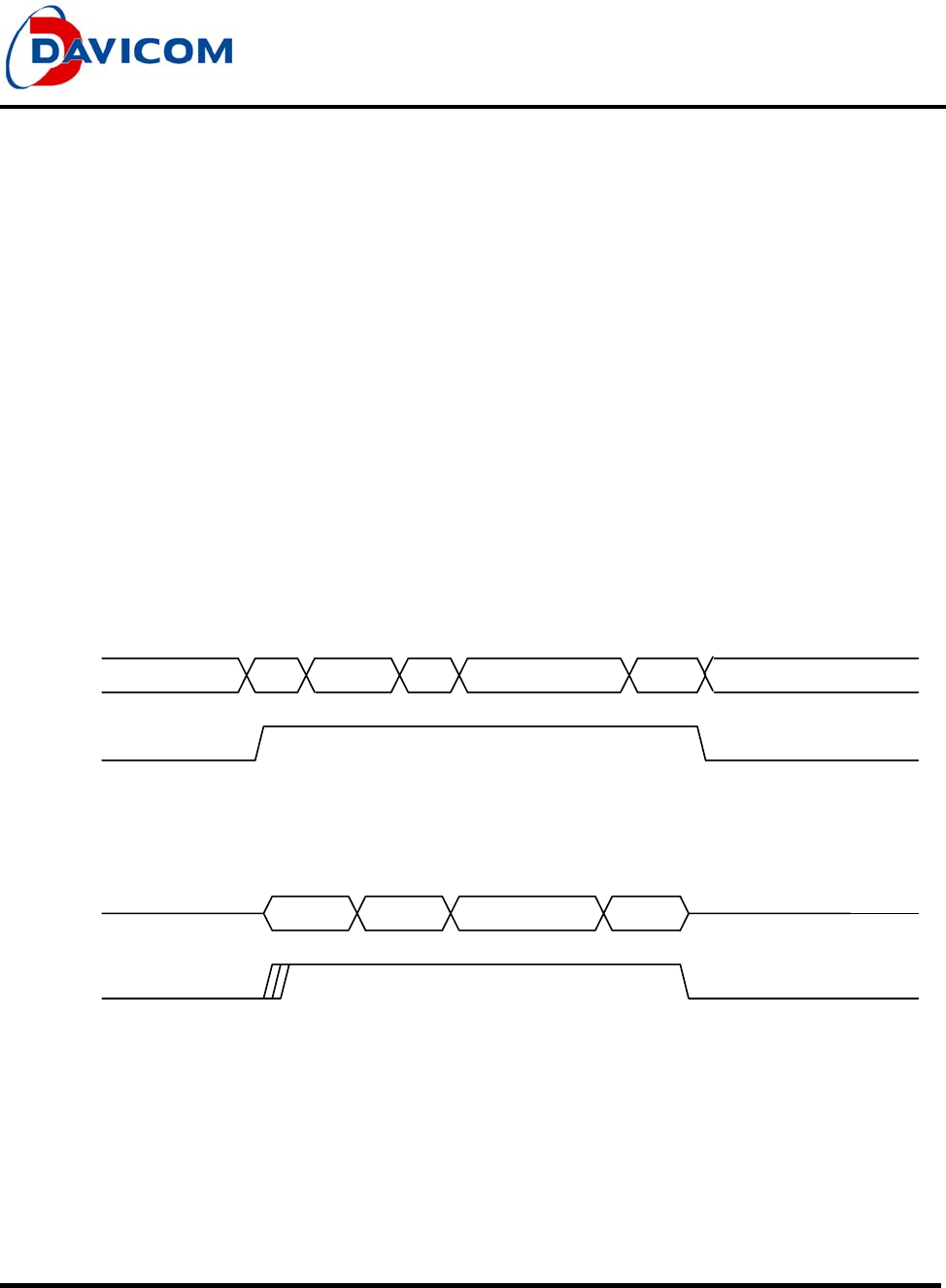

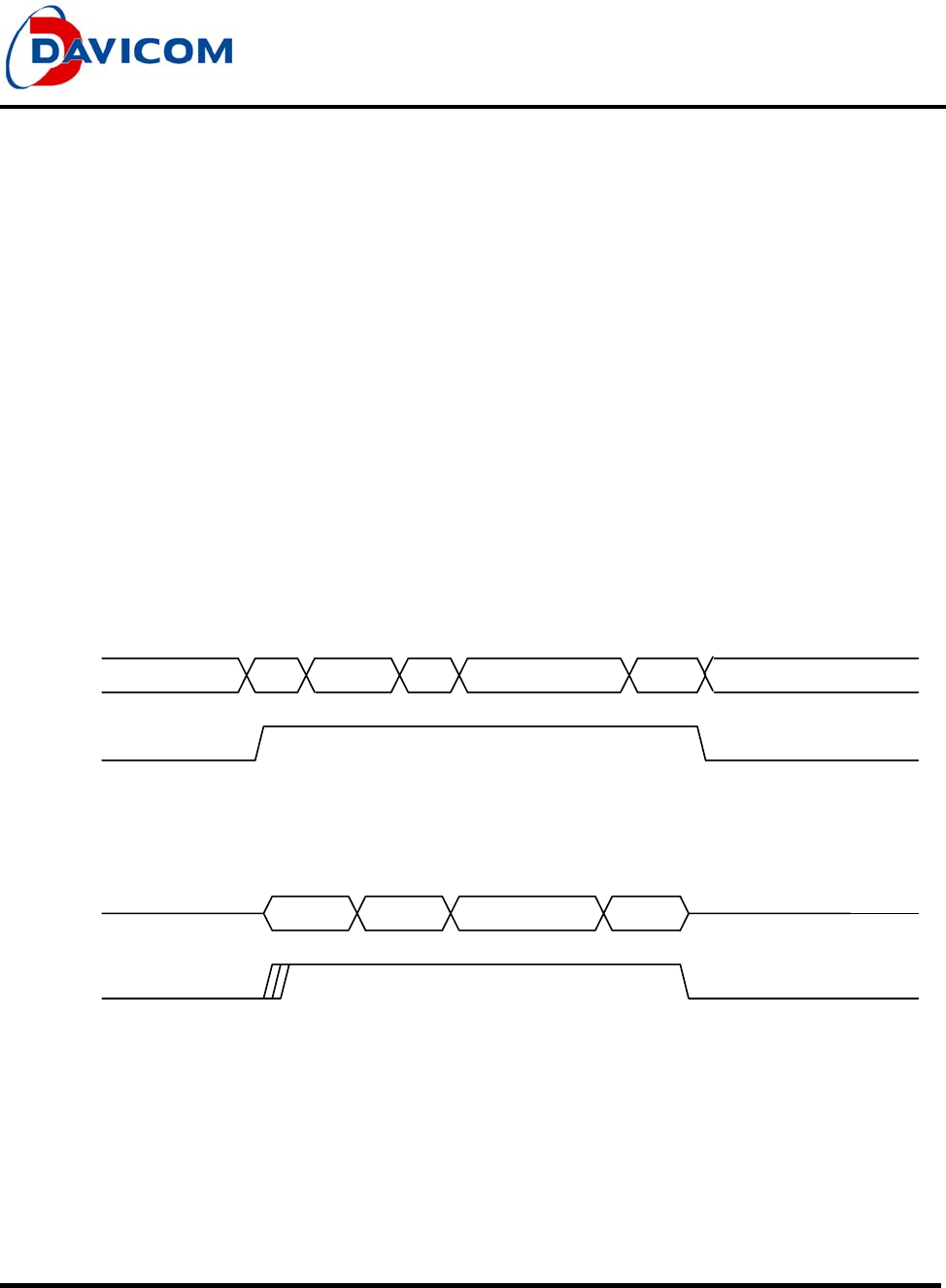

• CRS (carrier sense) is asserted by the PHY when either

the transmit or receive medium is non-idle, and

de-asserted by the PHY when the transmit and receive

medium are idle. Figure 7-2 depicts the behavior of

CRS during 10Base-T and 100Base-TX transmission.

TXD

Preamble SFD

Data

EFD

Preamble

SFD

Data

ESD

J/K

SSD

T/R

10Base-T

100Base-TX

TXD

CRS

CRS

IDLE

IDLE

Figure 7-2