4-39

Cisco 12010, Cisco 12410, and Cisco 12810 Router Installation and Configuration Guide

OL-11496-01

Chapter 4 System Startup and Basic System Configuration

Configuring the Software Configuration Register

High-Order Bits in the Software Configuration Register

This section describes the significance of high-order bits in the software

configuration register.

• Bit 8 of the software configuration register controls the console Break key.

–

Setting bit 8 causes the system to ignore the console Break key (factory

default).

–

Clearing bit 8 causes the system to interpret a Break keystroke as a

command to halt normal system operation and force the system into

ROM monitor mode.

Note Pressing the Break key during the first 5 seconds of system bootup causes

a return to the ROM monitor mode regardless of the setting of the Break

enable bit in the software configuration register.

• Bit 9 is not used.

• Bit 10 of the software configuration register controls the host portion of the

IP broadcast address.

–

Setting bit 10 causes the processor to use all zeros in the host portion of

the IP broadcast address

–

Clearing bit 10 causes the processor to use all ones (factory default)

Bit 10 interacts with bit 14, which controls the network and subnet portions

of the IP broadcast address.

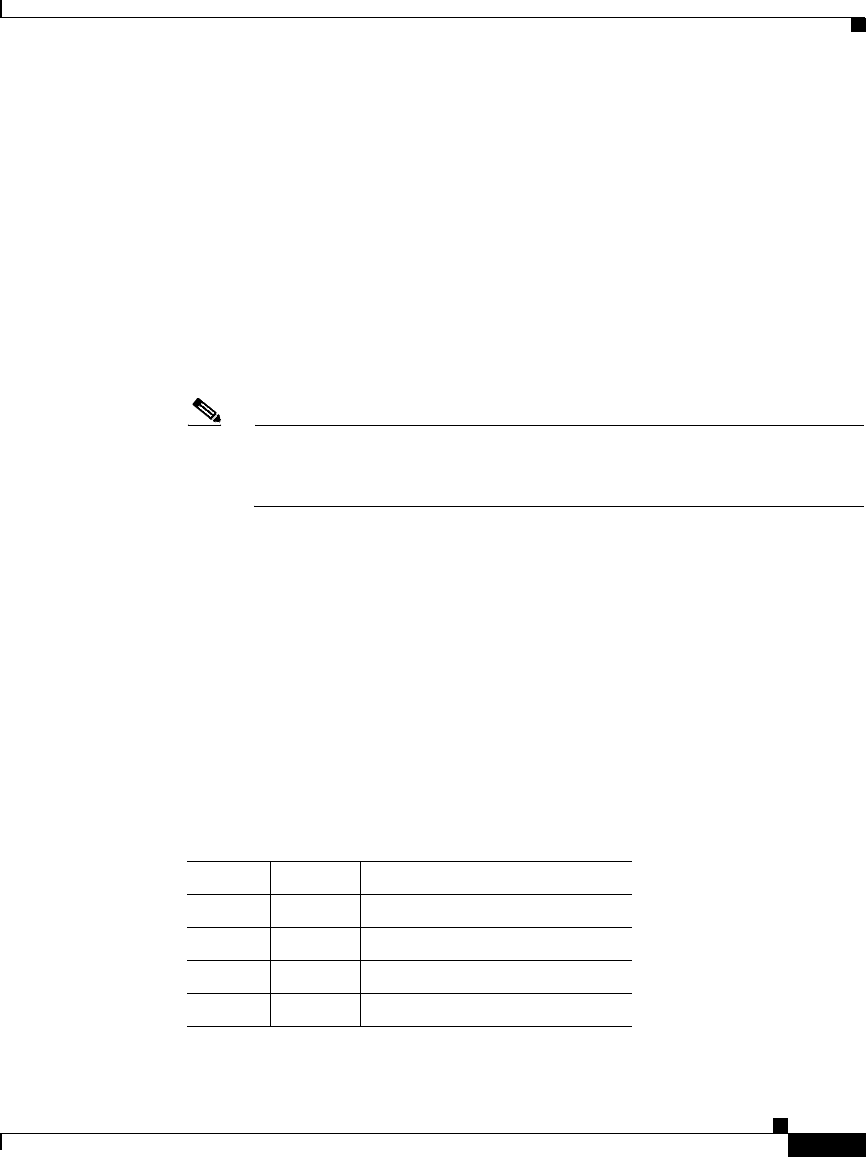

Table 4-7 shows the combined effect of bits 10 and 14.

Table 4-7 Configuration Register Settings for Broadcast Address Destination

Bit 14 Bit 10 Address (<net> <host>)

Off Off <ones> <ones>

Off On <zeros> <zeros>

On On <net> <zeros>

On Off <net> <ones>