4141

MDS-NT1

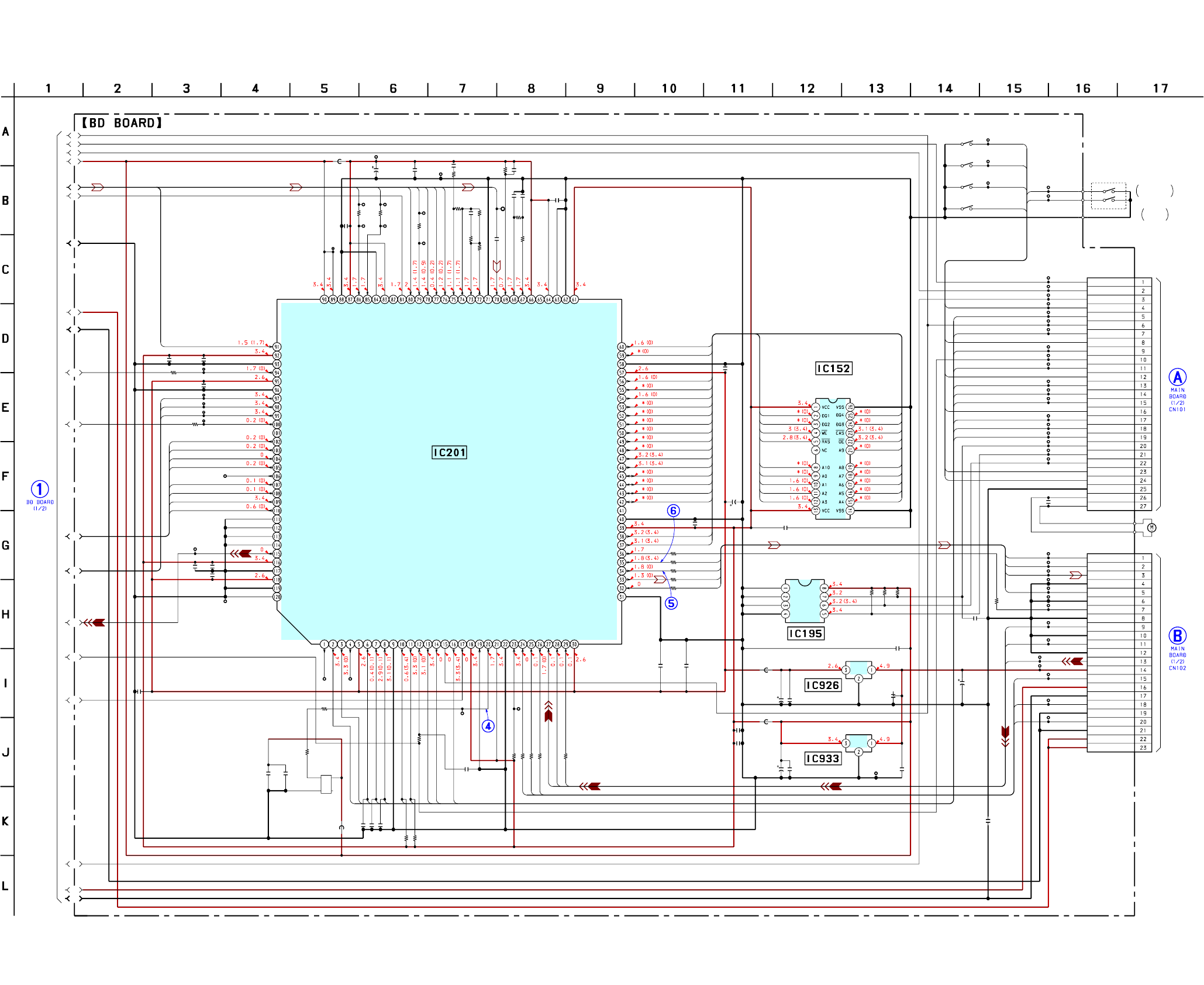

6-6. SCHEMATIC DIAGRAM – BD Board (2/2) –• See page 38 for Waveforms.

TP160

TP161

TP162

TP165

TP144

C233

TP942

TP941

TP940

TP939

TP938

TP937

TP936

TP934

TP933

TP932

TP930

TP929

TP928

TP926

TP925

TP924

TP923

TP922

TP921

TP917

TP916

TP986

TP911

TP914

TP913

TP912

TP987

TP899

TP999

TP910

TP909

TP908

TP907

TP919

TP920

TP927

TP931

TP935

R303R302 R301

C175

C901

IC926

IC933

C999

C998

TP169

C904

C242

C220

R214

R217

C221

TP146

R212 C219

R209

C215

R207

R208

C216 R211

R210

TP156

R201

TP113

TP1002

C240

R203

TP164TP145

TP125 TP101

R202

C206

C241

C903

C902

C908

C1102

C905

C255C254

TP190

R206R205

C214

TP110

TP158

R121

C251

R122

C235 C230

C250

C252

C809

C211C212

TP8

R218

R216

TP12

R219

C302

C253

C194

C301

C907

CN102

TP149TP148

TP10

C231

C234

R298

C209

S102

S101

S105

S104

S103

CN103

R178

M103

L801

L8

L10

R227

R226

R225

R224

R228

R299

R281

C807

R808

L899

X801

C205

L122

IC201

IC152

C909

TP1001

IC195

0.1

10k 10k 10k

0.1

100

6.3V

NJM2391DL1-26

BA033FP-E2

0.1

0.1

GND

0.1

0.1

0.47

100k

10k

0.01

330k 100p

330

0.033

150

1k

2.2 1M

33k

330

0.1

100680

100

6.3V

0.1

100

6.3V

0.1

10

0.1

100

6.3V

0.10.01

10k10k

0.01

2.2k

0.1

10k

0.1 0.1

0.1

0.1

4.7

100p100p

0

0

100

0.1

0.1

0.1

0.1

0.01

27P

0.1

0.1

0

100p

23P

0

100

100

100

100

100

0

1k

0.1

0

0

90MHz

0.0022

CXD2664R

MSM51V17400F-

50TS-K

22

10V

BR24C16F-E2

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

XOE

XCAS

XRAS

XWE

A00

A01

A02

A04

A05

A06

A07

A08

A09

A10

DTRF

CKRF

XLRF

M

N

T

1

M

N

T

2

S

Q

S

Y

D

Q

S

Y

X

IN

T

D

IN

0

D

IN

1

D

O

U

T

D

A

D

TI

L

R

C

K

I

X

B

C

K

I

DADTI

LRCKI

XBCKI

XBCK

LRCK

DADT

ADDT

MNT1

MNT2

SWDT

SCLK

XLAT

SRDT

SQSY

DQSY

XINT

SENS

A03

XWE

XOE

D0

D1

D2

D3

A00

A01

A02

A03

A04

A05

A06

A07

A08

A09

A10

XRAS

XCAS

TRDR

TFDR

FFDR

FRDR

SRDR

SFDR

SPRD

SPFD

XBCK

LRCK

DADT

ADDT

S

W

D

T

S

C

LK

X

L

A

T

S

R

D

T

S

E

N

S

DOUT

D

IN

0

D

IN

1

D1

D2D3

D0

B

B

1

B

B

2

B

B

3

B

B

4

B

B

5

B

B

6

BB7

B

B

8

BB9

CC1

CC2

CC3

CC4

CC5

CC6

CC1

CC2

CC3

CC4

CC5

CC6

MGND

SDA

SCL

GND

ADDT

M+5V

BCK

GND

H+5V

DADT

MGND

LRCK

+5V

DOUT

HGND

A2

A1

A0

DADTI

LRCKI

GND

XBCKI

DIN0

DIN1

MCKGND

MCLK

SRDT

XLATCH

SWDT

SCLK

WRPWR

SDA

MNT1(SHCK)

DQSY

DIG-RST

SQSY

SCL

XINT

MNT2(XBUSY)

LDON

MOD

LIMIT-IN

IOP

LD-IN

LD-OUT

EEP-WP

WP

VCC

M+5V

D-GND

PLAY-SW

REC-SW

OUT-SW

SENS

D-GND

GND

REFRECT SW

PROTECT SW

M

NT0(FOK)

M

NT1(SHCK)

M

NT2(XBUSY)

MNT3(SLOC)

VDC0

SW

DT

SCLK

XLAT

VSC0

SRDT

SENS

XRST

SQSY

RPW

R

XINT

XT

DQSY

VDIO0

OSCI

OSCO

OSCN

VSIO0

XTSL

DIN0

DIN1

DOUT

DATA1

LRCKI

XBCK

I

VDC1

VSC1

ADDT

DADT

LRCK

XBCK

XWE

XOE

DRVDD0

DRVSS0

A11

D3

D2

D0

D1

XCAS

XRAS

A09

A08

A10

A07

A00

A06

A01

A05

A02

VDC2

VSC2

A04

A03

DRVDD1

DRVSS1

TEST0

TEST1

TEST2

AVD1

ASYO

ASYI

BIAS

RFI

AVS1

PCO

FILI

FILO

CLTV

PEAK

BOTM

ABCD

FE

AUX1

VC

ADIO

ADRT

ADRB

SE

TE

AVD2

AVS2

DCHG

APC

ADFG

VDIO1

VSIO1

F0CN

VSC3

VDC3

XLRF

CLRF

DTRF

APCR

LDDR

TRDR

TFDR

FFDR

FRDR

FS4

SRDR

SFDR

SPRD

SPFD

FGIN

TST1

TST2

TST3

EFMO

VDIO2

VSIO2

VDC4

VSC4

MDDT1

FS256

(2/2)

-1

-2

S102-1

REFLECT RATE

DETECT

DETECT

PROTECT

S102-2

(LIMIT IN)

(OUT)

(PLAY)

(REC)

(LOADING)

G

OI

G

OI

+3.3V REGULATOR

+2.6V REGULATOR

EEPROM

DIGITAL SERVO SIGNAL PROCESSOR,

DIGITAL SIGNAL PROCESSOR,

EFM/ACIRC ENCODER/DECODER,

SHOCK PROOF MEMORY CONTROLLER,

ATRAC ENCODER/DECODER

1

3

4

2

D-RAM

(NOT SUPPLIED)

(Page 40)

(Page 44)

(Page 44)