Specifications

TDS5000B Series Specifications and Performance Verification

1-17

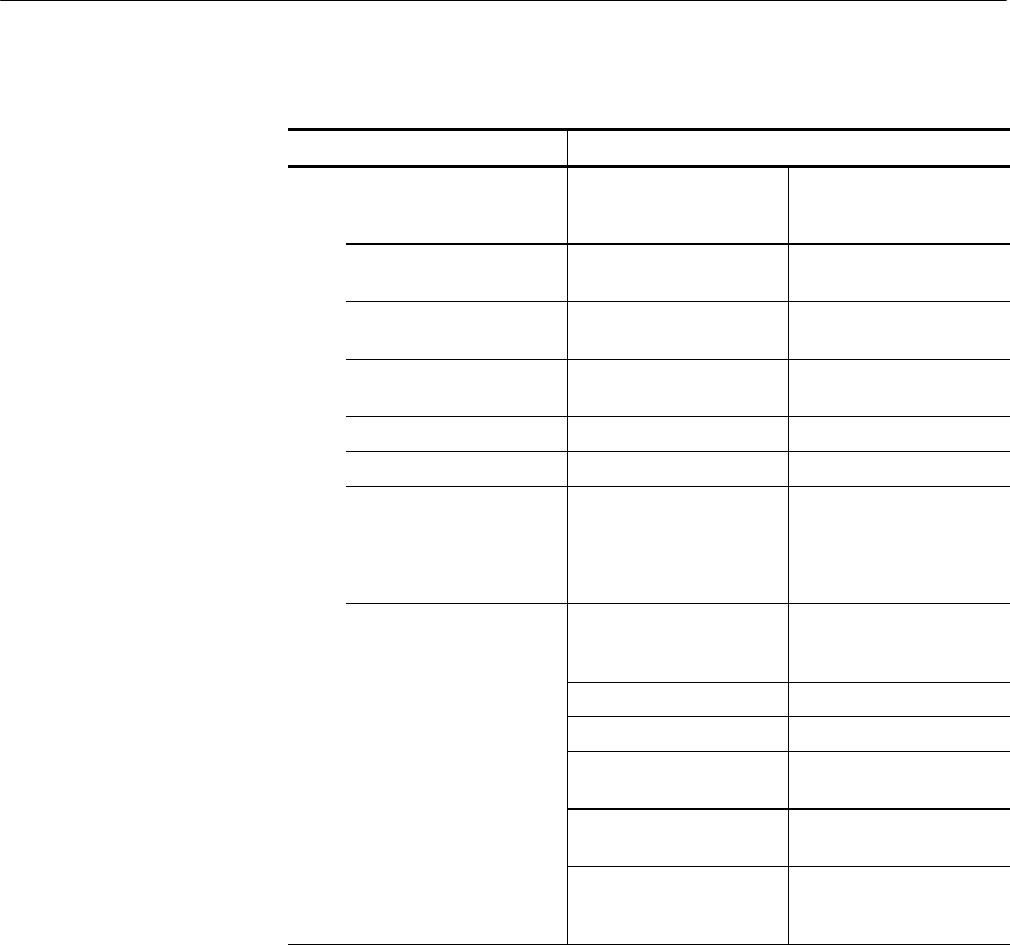

Table 1-4: Trigger specifications (Cont.)

Characteristic Description

Width type Minimum difference

between upper and lower

limits = 1 ns

2 ns + 5% of upper limit

setting

Timeout type Minimum ti meout time =

1ns

2 ns + 5% of timeout set-

ting

Transition type Minimum transition time =

600 ps

8.5 ns + 5% of transition

time setting

Pattern type, typical Minimum time the pattern is

true = 1 ns

1ns

Logic Not applicable 1ns

Events Delay 1 ns (single channel) Not applicable

State t ype, typical Minimum true time before

clock edge = 1 ns

Minimum true time after

clock edge = 1 ns

1ns

Setup/Hold t y pe, typical Minimum clock pulse width

from acti ve edge to inactive

edge

Minimum clock pulse width

from inact ive edge to active

edge

3 ns + hold time setting 2ns

Setup and Hold parameters Limits

Setup time (time from data

transition t o cl ock edge)

--100 ns minimum

+100 ns maximum

Hold time (time from clock

edge to data transition)

--1 ns minimum

+102 ns maximum

Setup time + Hold time

(algebraic sum of the two

settings)

+2 ns minimum

+202 ns maximum