App-49

8

8

8

8

A

6

7

8

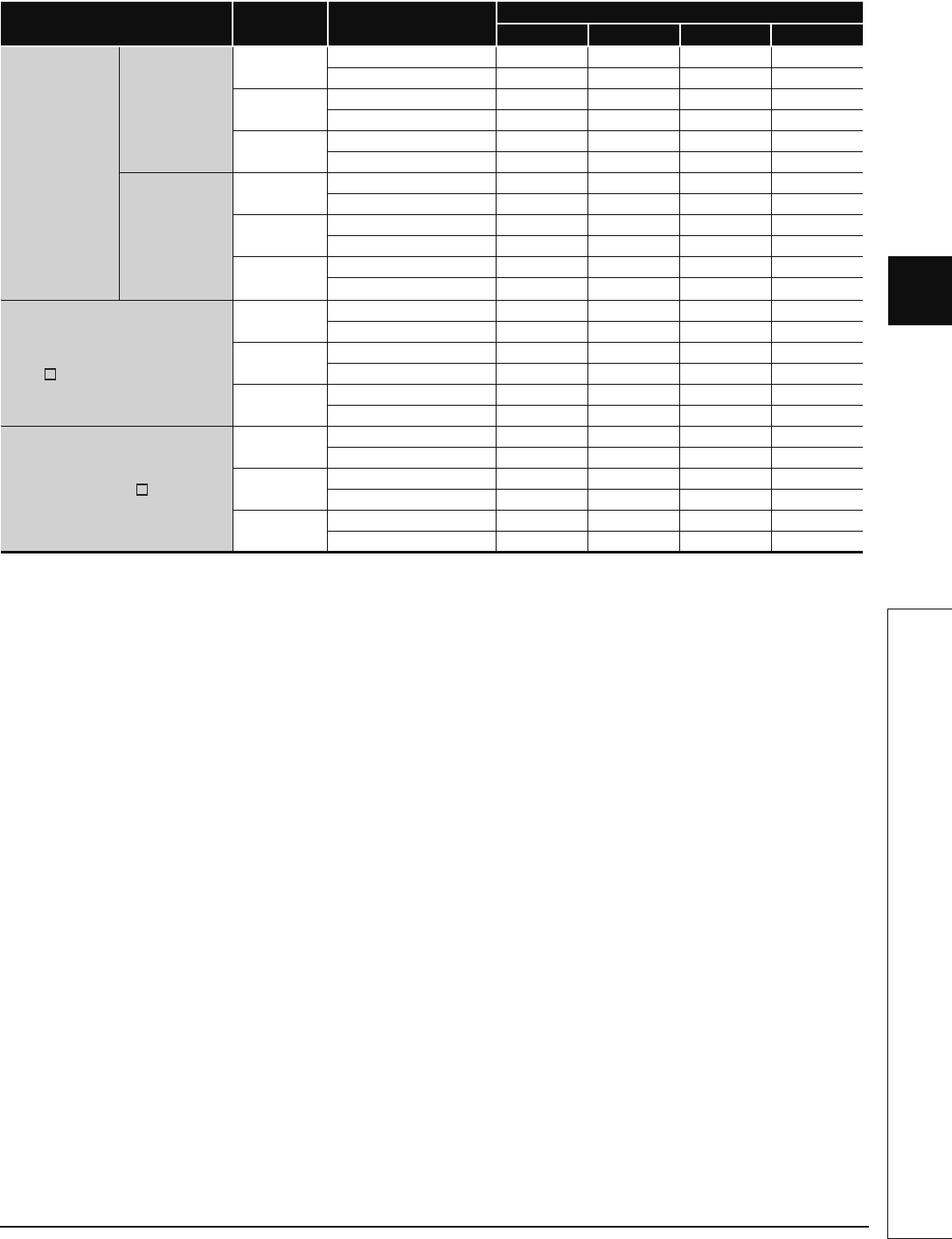

Appendix1 OPERATION PROCESSING TIME

Appendix 1.3

Operation Processing Time of High Performance Model QCPU/Process CPU/Redundant CPU

(6) Table of the time to be added when file register, module access device or link direct device is

used

Instruction data

Device Specification

Location

Processing Time (µs)

Qn QnH QnPH QnPRH

File register (ZR)

When standard

RAM is used

Bit

Source 5.56 2.40 2.40 2.40

Destination 4.44 1.91 1.91 1.91

Word

Source 2.60 1.12 1.12 1.12

Destination 3.76 1.62 1.62 1.62

Double word

Source 2.83 1.22 1.22 1.22

Destination 4.00 1.72 1.72 1.72

When SRAM

card is used

(Q2MEM-1MBS,

Q2MEM-2MBS)

Bit

Source 5.22 2.25 2.25 2.25

Destination 4.09 1.76 1.76 1.76

Word

Source 2.25 0.97 0.97 0.97

Destination 3.42 1.47 1.47 1.47

Double word

Source 2.49 1.07 1.07 1.07

Destination 3.65 1.57 1.57

1.57

Module access device

(Un\G , U3En\G0 to G4095)

Bit

Source 35.56 15.31 15.31 15.31

Destination 65.08 28.01 28.01 28.01

Word

Source 32.76 14.10 14.10 14.10

Destination 28.84 12.41 12.41 12.41

Double word

Source 32.99 14.20 14.20 14.20

Destination 29.07 12.51 12.51 12.51

Link direct device (Jn\ )

Bit

Source 75.67 32.57 32.57 32.57

Destination 138.65 59.67 59.67 59.67

Word

Source 72.73 31.30 31.30 31.30

Destination 137.32 59.10 59.10 59.10

Double word

Source 72.96 31.40 31.40 31.40

Destination 137.55 59.20 59.20 59.20