10-15

D(P).DDWR

7

10

7

7

7

7

7

7

10.2 Writing Devices to Another CPU (D(P).DDWR)

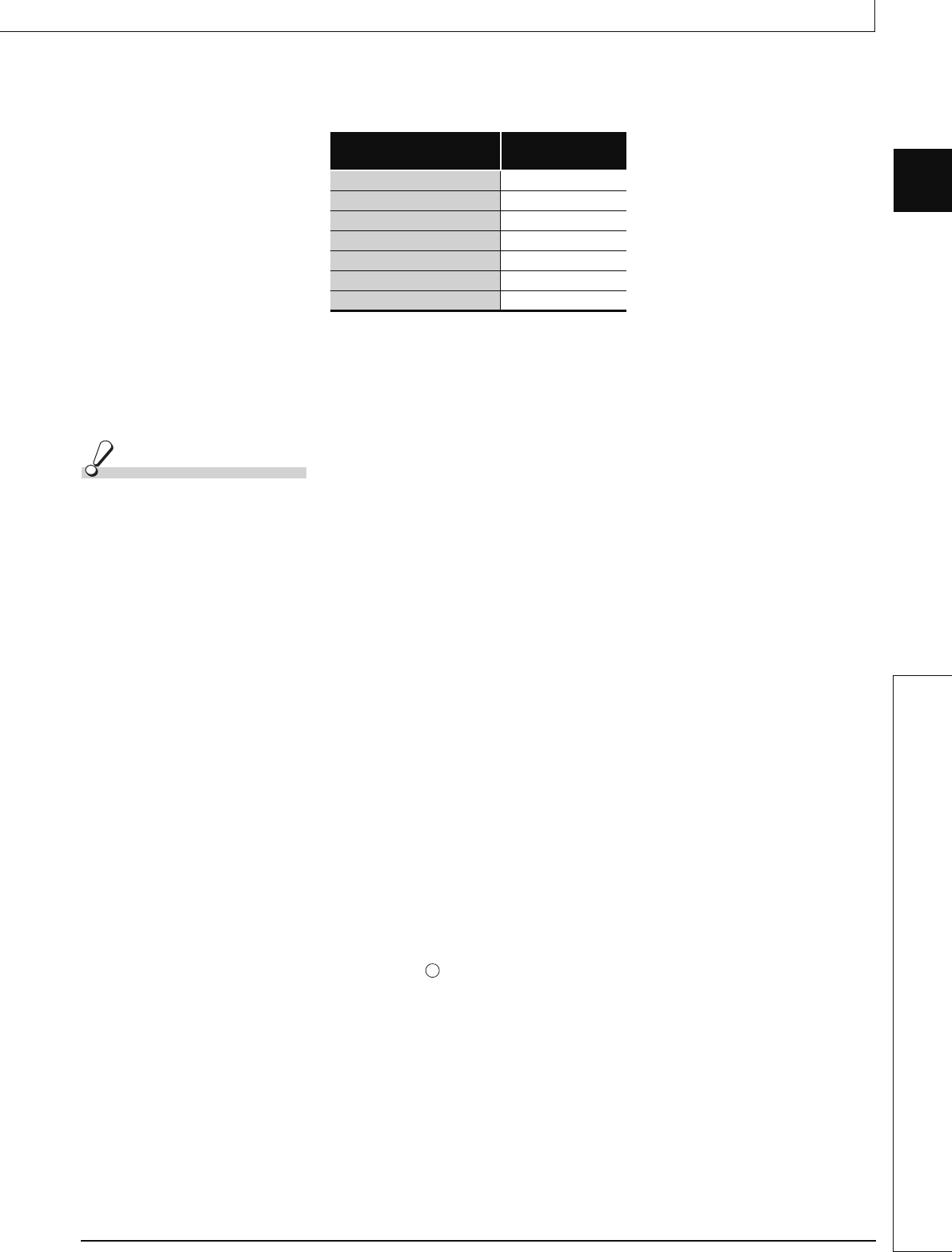

(3) The number of blocks used for the instruction depends on the number of write points (refer

to Section 12.1).

Number of blocks used for the instruction

(4) The instruction will be completed abnormally when there are no empty blocks in the multiple

CPU high speed transmission area.

Set the number of blocks used for the instruction at special registers (SD796 to SD799), and

use the special relays (SM796 to SM799)as an interlock prevent error completion (refer to

Section 12.1).

Operation Error

In any of the following cases, an operation error occurs, the error flag (SM0) turns on, and an

error code is stored into SD0.

(1) Specified another CPU is wrong or the multiple CPU high-speed transmission dedicated

instruction cannot be used in the setting (Error code: 4350)

• The reserved CPU has been specified.

• Unmounted CPU has been specified.

• Another CPU start I/O number divided by 16n is out of 3E0

H to 3E3H.

• The instruction was executed without setting "Use multiple CPU high speed

transmission".

• The instruction was executed with the Q02UCPU.

• Host CPU has been specified.

• The CPU where the instruction cannot be executed has been specified.

(2) The instruction cannot be executed with the CPU. (Error code: 4351)

• Another CPU does not support this instruction.

(3) The number of devices is wrong. (Error code: 4352)

(4) The device that cannot be used for the instruction has been specified. (Error code: 4353)

(5) A device has been specified by the character string that cannot be used. (Error code: 4354)

(6) The number of write points ( +1)is other than 0 to 100. (Error code 4354)

Number of write points

specified by the instruction

D(P).DDWR

instruction

1 to 4 1

5 to 20 2

21 to 36 3

37 to 52 4

53 to 68 5

69 to 84 6

85 to 100 7

S1