2-25

2

3

4

4

6

7

8

2.4 Basic instructions

2.4.4 Data transfer instructions

Table 2.13 Data Transfer Instructions (Continued)

*1: The number of steps may vary depending on the device and type of CPU module being used.

Note 1) The number of steps may increase due to the conditions described in Section 3.8.

*2: The number of steps may vary depending on the device and type of CPU module being used.

Note 1) The number of steps may increase due to the conditions described in Section 3.8.

Category

Instruction Symbol

Symbol Processing Details

Execution

Condition

Number of Basic Steps

Subset

See for Description

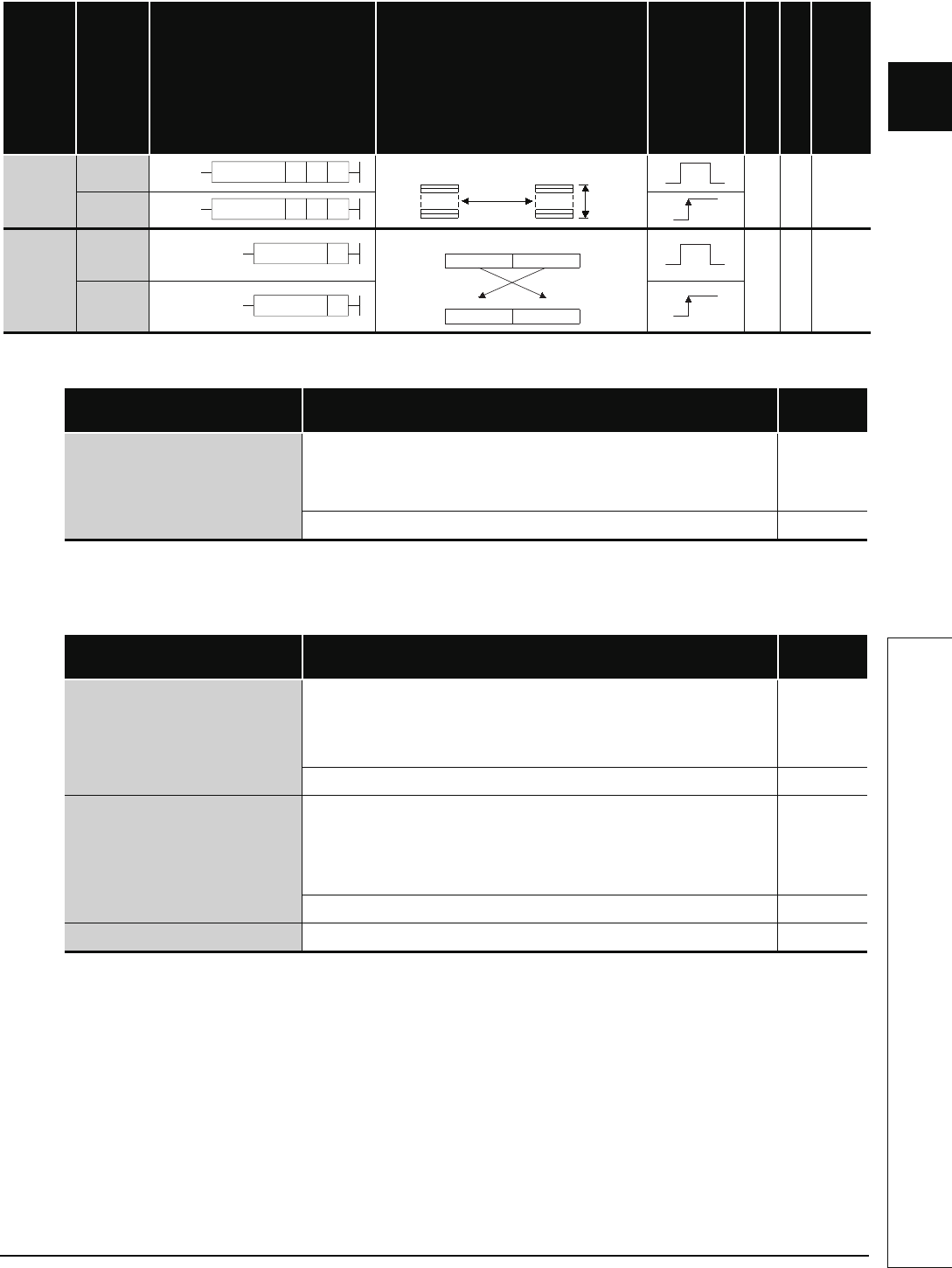

Block data

exchange

BXCH

4 - 6-126

BXCHP

Exchange

of upper

and lower

bytes

SWAP

3 - 6-128

SWAPP

Component Device

Number of

Steps

QCPU

• Word device: Internal device (except for file register ZR)

• Bit device: Devices whose device Nos. are multiples of 16, whose digit

designation is K4, and which use no indexing.

• Constant: No limitations

2

Devices other than above

3

Note 1)

Component Device

Number of

Steps

High Performance model QCPU

Process CPU

Redundant CPU

• Word device: Internal device (except for file register ZR)

• Bit device: Devices whose device Nos. are multiples of 16, whose

digit designation is K8, and which use no

indexing.

• Constant: No limitations

3

Devices other than above

3

Note 1)

Basic model QCPU

• Word device: Internal device (except for file register ZR)

• Bit device: Devices whose device Nos. are multiples of 16, whose digit

designation is K8, and which use no indexing.

• Constant: No limitations

(The number of steps is 3 when the above device + constant are used.)

2

Devices other than above

3

Note 1)

Universal model QCPU All devices that can be used

2

Note 1)

BXCH nSD

n

(S)

(D)

BXCHP nSD

SWAP D

b0b15to tob8 b7

b0b15to

to

8 bits

b8 b7

(D)

(S)

8 bits

8 bits 8 bits

SWAPP D