App-195

8

8

8

8

A

8

7

8

Appendix 4 SPECIAL REGISTER LIST

*2 : Shows the special register (SD ) for the host system CPU.

TableApp.4.20 Special register

Number Name Meaning Explanation

Set by

(When Set)

Corres-

ponding

ACPU

SD *2

Corresponding

CPU

SD1649

Standby system

error cancel

command

Error code of error

to be cleared

• Stores the error code of the error to be cleared by clearing a standby

system error.

• Stores the error code of the error to be cleared into this register and turn

SM1649 from OFF to ON to clear the standby system error.

• The value in the lowest digit (1 place) of the error code is ignored when

stored into this register.

(By storing 4100 in this register and resetting the error, errors 4100 to

4109 can be cleared.)

S(Every END)

–QnPRH

SD1650

Other system

operating

information

Other system

operating

information

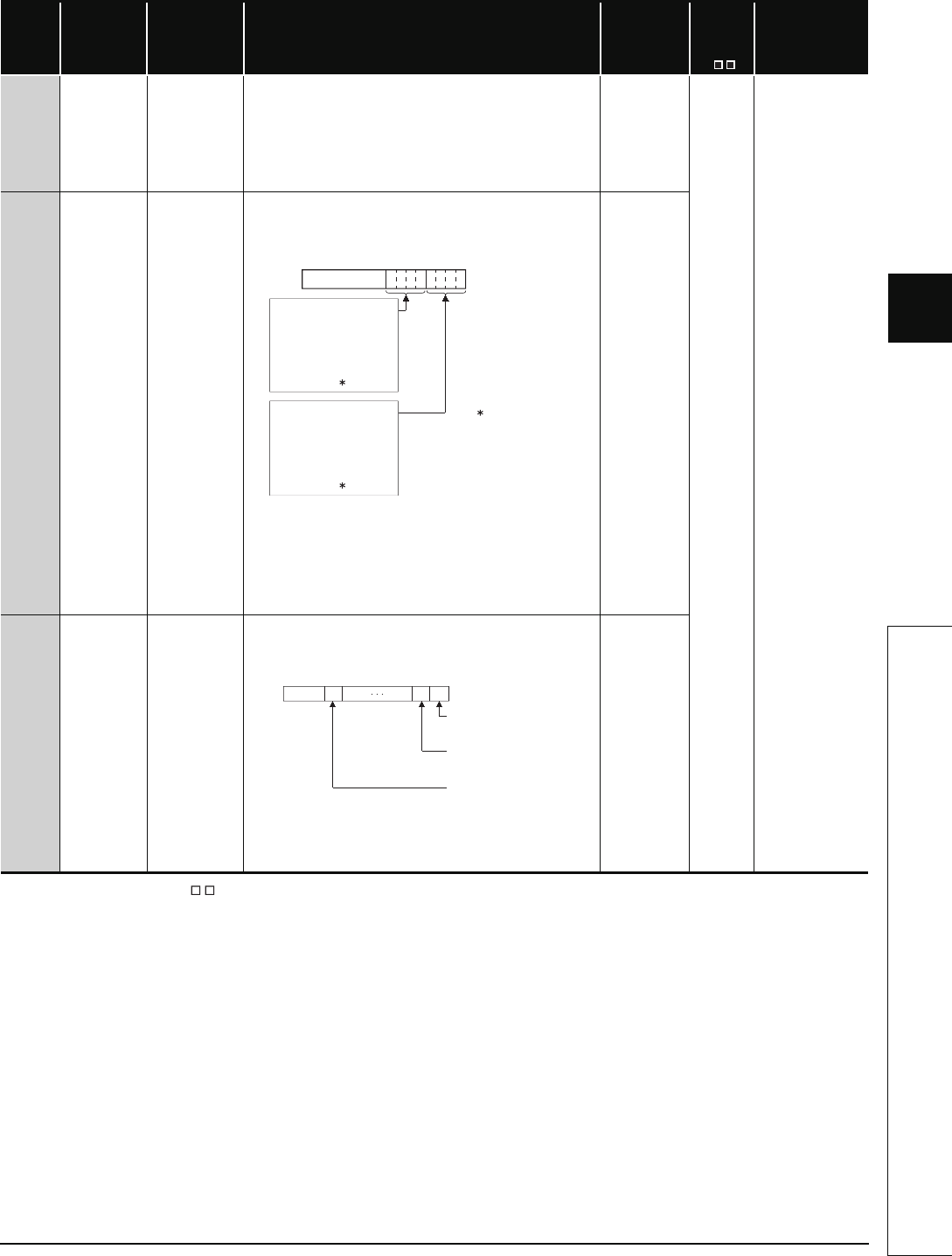

Stores the operation information of the other system CPU module in the

following format.

"00FFH" I stored when a communication error occurs, or when in debug

mode.

Note : A communication error is caused by the following:.

• When the power supply is switched off, or when the other system is

reset.

• H/W error occurs on either of system A or B.

• WDT error occurs.

• Tracking cable is not connected.

• Tracking cable is disconnected or damaged.

S(Every END)

SD1690

Network module

head address,

which requested

system

switching on

host (control)

system

Network module

head address,

which requested

system switching

on host (control)

system

• Stores head address of network module which a system switch request

was initiated, using the following format.

• Turns off automatically by system, after network error is reset by user.

• Please refer to SD1590 which stores the corresponding head address of

network module on host system.

S(Every END)

0:No error

1:Continue error

2:Stop error

F:Communication with

other system

disabled

0:RUN

2:STOP

3:PAUSE

F:Communication with

other system

disabled

: Communication

with other system

disabled, debug

mode

b15 to tob8 b4b7 tob3 b0

0

SD1650

)

(

)

(

to

b1 b0

b15 b11to to

0

0/1

0/10

Module 0: CPU module is

invalid as it is 2-

slot model

Module 1:Module on the

right side of the

CPU module

Module11:Module at the

rightmost end of

the 12-slot base

(Q312B)

SD1690

Each bit

0:OFF

1:ON