10-7

7

10

7

7

7

7

7

7

10.1 Overview

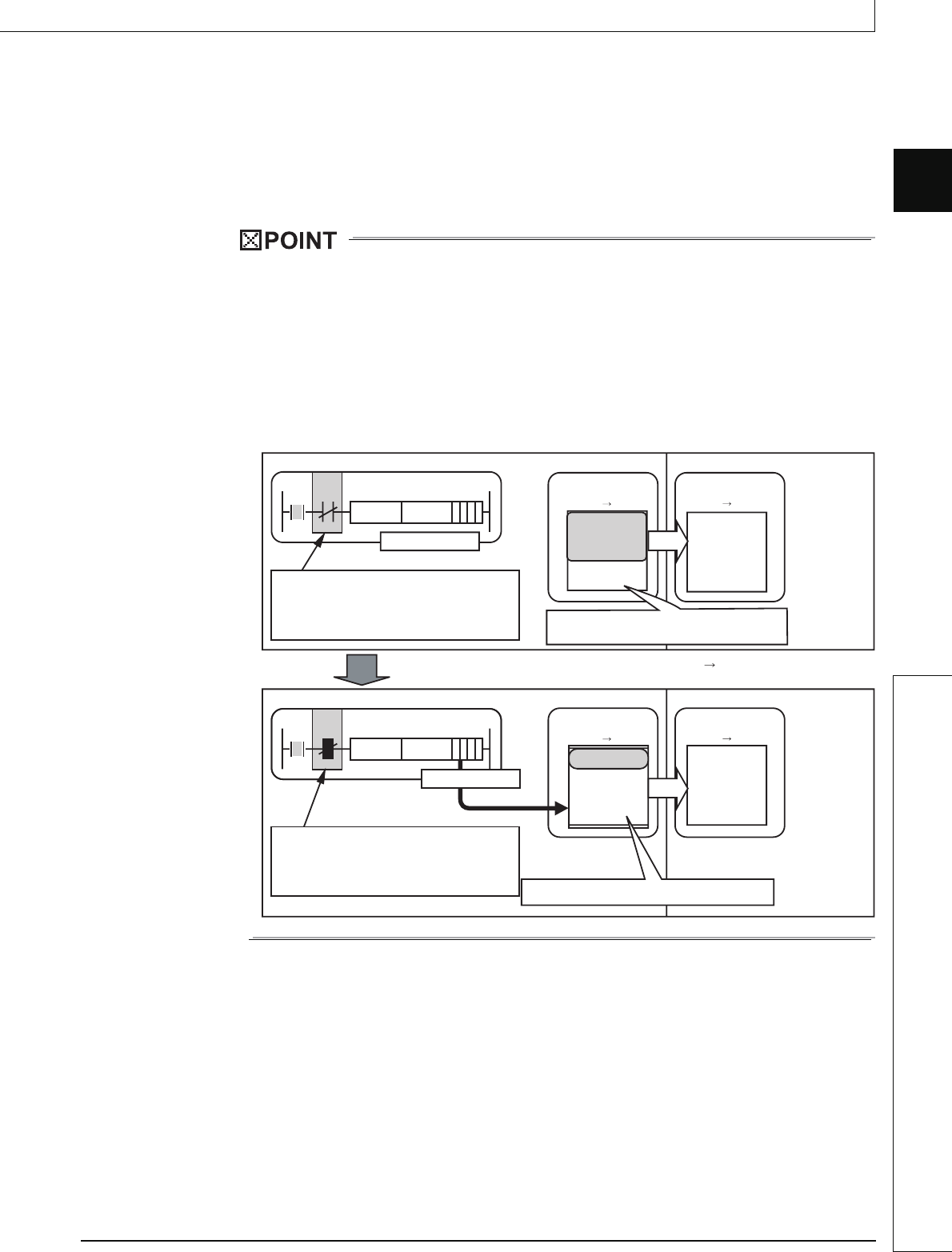

(7) Interlock when using the multiple CPU high-speed transmission dedicated instruction

(a) Special relays SM796 to SM799 (maximum number of used blocks for multiple CPU

high-speed transmission dedicated instruction setting) can be used as an interlock for

the multiple CPU high-speed transmission dedicated instruction.

When executing the multiple CPU high-speed transmission dedicated instructions

concurrently, use SM796 to SM799 as an interlock for the instructions.

When using special relays SM796 to SM799, set the maximum number of blocks

for the instruction used for each CPU to special registers SD796 to SD799. (For

example, when the maximum number of blocks for the multiple CPU high-speed

transmission dedicated instruction to be executed to CPU No.3 is 5, set 5 to

SD798.)

When the multiple CPU high speed transmission area becomes equal to or less

than the number of blocks set at SD796 to SD799, the corresponding special

relay (SM796 to SM799) turns on.

CPU No.1

CPU No.2

Execution

command

SM

797

DP.DDWR

H3E1

Number of request blocks:4

Turns on when the number of empty blocks

is less than the number of blocks used for

the DP.DDWR instruction.

(The DP.DDWR instruction is not executed.)

Multiple CPU high speed transmission area Multiple CPU high speed transmission area

Send area

(1 2)

Receive area

(1 2)

During use

Number of empty blocks:

2

Lnsufficient for writing a request from

the DP.DDWR instruction.

Empty area of the request blocks in send area (1 2) has been increased.

CPU No.1

CPU No.2

Execution

command

SM

797

DP.DDWR

H3E1

Number of request blocks:4

Multiple CPU high speed transmission area Multiple CPU high speed transmission area

Send area

(1 2)

Receive area

(1 2)

During use

Number of empty blocks:

8

Turns off as empty blocks by the number of blocks

used for the DP.DDWR instruction became available

(The DP.DDWR instruction can be written.)

The request from the DP.DDWR instruction can be written.