6-47

E+(P),E-(P)

1

2

3

4

4

6

7

8

6.2 Arithmetic Operation Instructions

6.2.9 Addition and subtraction of floating decimal point data (Single precision) (E+(P),E-(P))

(2) Values which can be designated at and and which can be stored, are as follows:

0, 2

-126

| Designated value (stored value) | < 2

128

Operation Error

(1) In any of the following cases, an operation error occurs, the error flag (SM0) turns ON, and

an error code is stored into SD0.

• The contents of the designated device or the result of the addition are not "0", or not within

the following range: (Error code: 4100)

0, 2

-126

| Contents of designated device | < 2

128

(For the Basic model QCPU, High Performance model QCPU, Process CPU, Redundant

CPU) (Error code: 4100)

• The value of the specified device is 0.

*2

(For the Basic model QCPU, High Performance model QCPU, Process CPU, Redundant

CPU) (Error code: 4100)

*2: There are CPU modules that will not result in an operation error if 0 is specified.

Refer to Section 3.2.4 for details.

• The result of addition and subtraction exceeds the following range. (The overflow occurs.)

(For the Universal model QCPU only)

2

128

| Result of addition and subtraction | (Error code: 4141)

• The value of the specified device is 0, unnormalized number, nonnumeric, and ± .

(For the Universal model QCPU only) (Error code: 4140)

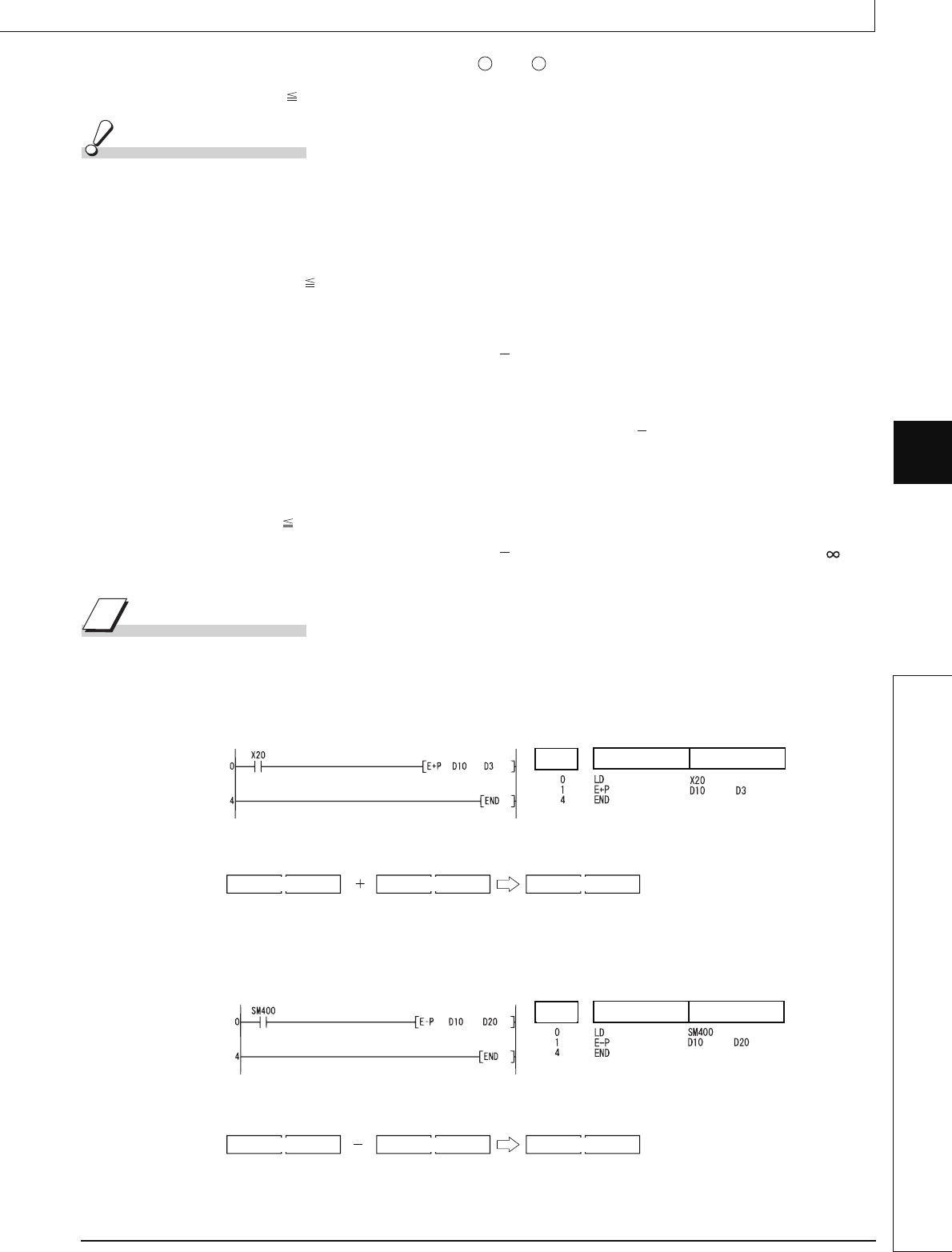

Program Example

(1) The following program adds the 32-bit floating decimal point type real numbers at D3 and D4

and the 32-bit floating decimal point type real numbers at D10 and D11 when X20 goes ON,

and stores the result at D3 and D4.

[Ladder Mode] [List Mode]

[Operation]

(2) The following program subtracts the 32-bit floating decimal point type real number at D10

and D11 from the 32-bit floating decimal point type real numbers at D20 and D21, and stores

the result of the subtraction at D20 and D21.

[Ladder Mode] [List Mode]

[Operation]

S

D

Step

Instruction

Device

D4

5961.437

D3

D11

12003.200

D10

D4

17964.637

D3

Step

Instruction

Device

D21

97365.203

D20 D11

76059.797

D10 D21

21305.406

D20