6-134

DI,EI,IMASK

IMASK

(1) Enables/disables the execution of the interrupt program marked by the designated interrupt

pointer by using the bit pattern of 8 points from the device designated by .

• 1(ON)......Interrupt program execution enabled

• 0(OFF)....Interrupt program execution disabled

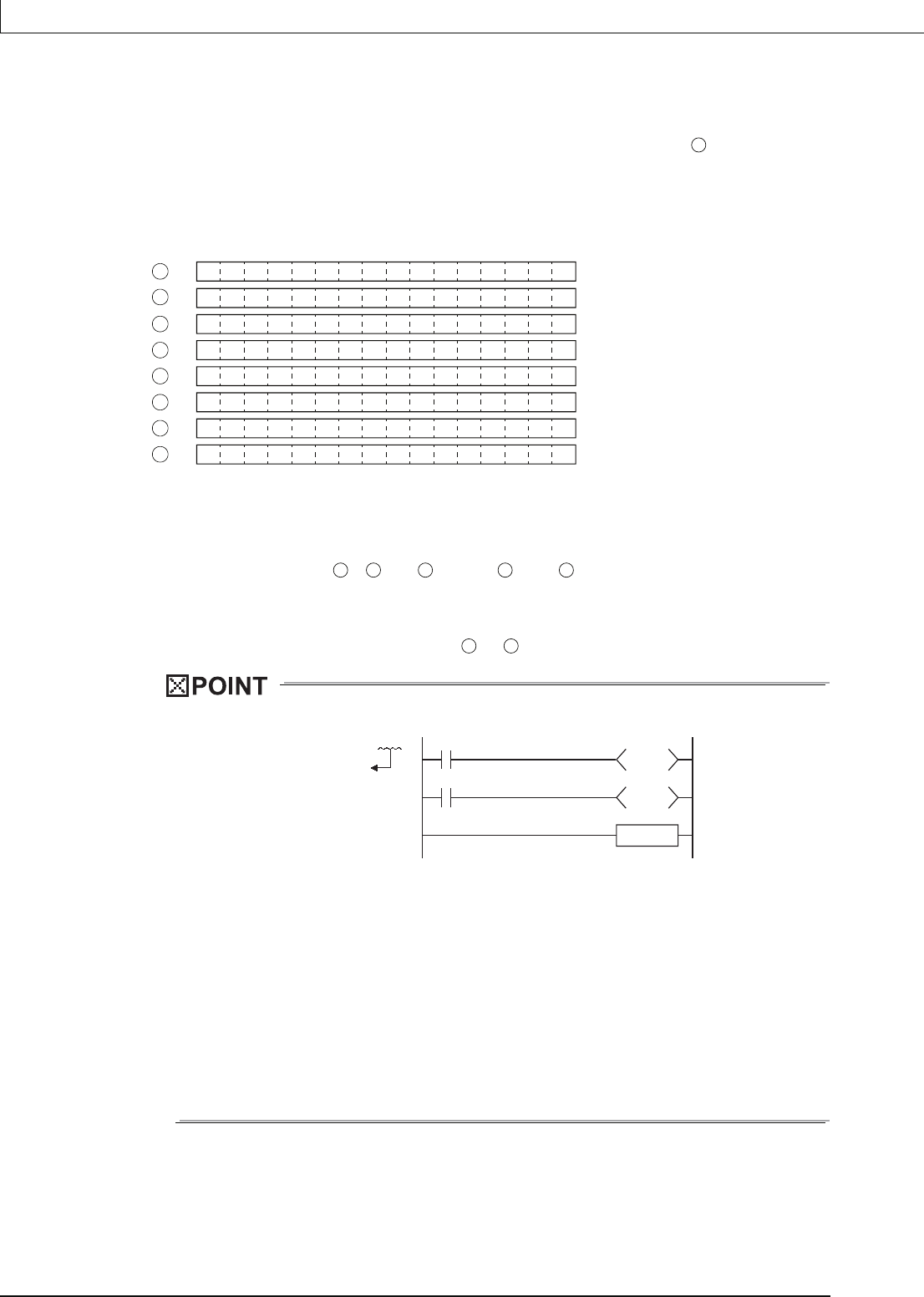

(2) The interrupt pointer numbers corresponding to the individual bits are as shown below:

(3) When the power is turned ON or when the CPU module has been reset, the execution of

interrupt programs I0 to I31,I48 to I127 is enabled, and the execution of interrupt programs

I32 to I47 is disabled.

(4) The statuses of devices , +1, +2, and +3 to +7 are stored in SD715 to SD717

and SD781 to SD785 (storage area for the IMASK instruction mask pattern).

(5) Although the special registers are separated as SD715 to SD717 and SD781 to SD785,

device numbers should be designated as to +7 successively.

1. An interrupt pointer occupies 1 step.

2. For the information on interrupt conditions, link direct devices, refer to the

QnUCPU User’s Manual(Function Explanation, Program Fundamentals) or

Qn(H)/QnPH/QnPRHCPU User’s Manuall(Function Explanation, Program

Fundamentals)

3. The DI state (interrupt disabled) is active during the execution of an interrupt

program. Do not insert the EI instructions in interrupt programs to attempt the

execution of multiple interrupts, with interrupt programs running inside interrupt

programs.

4. If there are the EI and DI instructions within a master control, these instructions

will be executed regardless of the execution/non-execution status of the MC

instruction.

S

b15

I15 I14

b0

I13 I12 I11 I10 I9 I8 I7 I6 I5 I4 I3 I2 I1 I0

b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1

I31 I30 I29 I28 I27 I26 I25 I24 I23 I22 I21 I20 I19 I18 I17 I16

I47 I46 I45 I44 I43 I42 I41 I40 I39 I38 I37 I36 I35 I34 I33 I32

+ 1

+ 2

S

S

S

I63 I62 I61 I60 I59 I58 I57 I56 I55 I54 I53 I52 I51 I50 I49 I48

+ 3

S

I79 I78 I77 I76 I75 I74 I73 I72 I71 I70 I69 I68 I67 I66 I65 I64

+ 4

S

I95 I94 I93 I92 I91 I90 I89 I88 I87 I86 I85 I84 I83 I82 I81 I80

+ 5

S

I111 I110 I109 I108 I107 I106 I105 I104 I103 I102 I101 I100 I99 I98 I97 I96

+ 6

S

I127 I126 I125 I124 I123 I122 I121 I120 I119 I118 I117 I116 I115 I114 I113 I112

+ 7

S

S S S S S

S S

X1C

55

53

50

Y10

Y30

X5

Stored at step 50

IRET

I10