9-5

S(P).TO

9

7

7

7

7

7

7

7

9.1 Writing to the CPU Shared Memory of Host CPU

9.1.1 Write to Host CPU Shared Memory (S(P).TO)

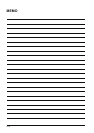

(a) CPU shared memory address of the Basic model QCPU

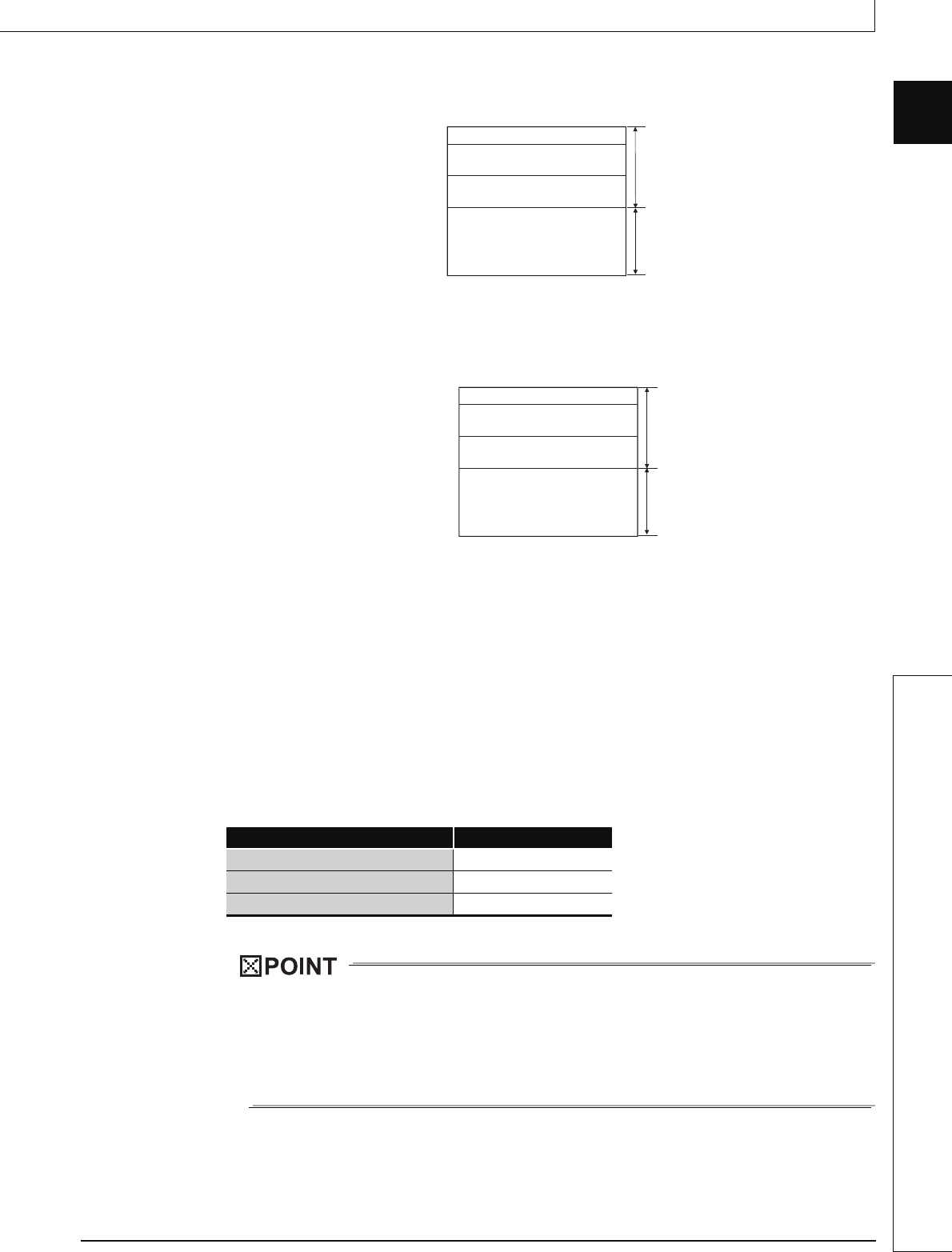

(b) CPU shared memory address of the High Performance model QCPU, Process CPU and

Universal model QCPU*

4

*3 : Usable as a user free area when auto refresh setting is not made.

In addition, even when auto refresh setting is made, the auto refresh send range or later is

usable as a user free area.

*4 : Data cannot be written to the multiple CPU high speed transmission area of the Universal

model QCPU with the S(P).TO instruction.

(2) When the number of write points is 0, no processing is performed and the completion device

does not turn ON, either.

(3) The S.TO instruction can be executed once to one scan for each CPU.

When execution condition is established at two or more places at the same time, the S.TO

instruction executed later is not processed since handshake is established automatically.

(4) The number of data that can be written varies depending on the target CPU module.

Writing data to CPU shared memory can be performed using the intelligent

function module device.

For intelligent function module device, refer to the QnUCPU User's Manual

(Function Explanation, Program Fundamentals) or Qn(H)/QnPH/QnPRHCPU

User's Manual (Function Explanation, Program Fundamentals).

CPU module Number of Write Points

Basic model QCPU

1 to 320

High Performance model QCPU Process CPU

1 to 256

Universal model QCPU

1 to 2048

Host CPU operation information area

CPU shared memory address

System area

Host CPU refresh area

*3

User free area

0(0

H)

96(60

H)

192(C0

H)

511(1FFH)

Write designation

prohibited area

Write designation

permitted area

CPU shared memory address

0(0

H)

512(200

H)

2048(800

H)

4095(0FFFH)

Host CPU operation information area

System area

Host CPU refresh area

*3

User free area

Write designation

prohibited area

Write designation

permitted area