10-12

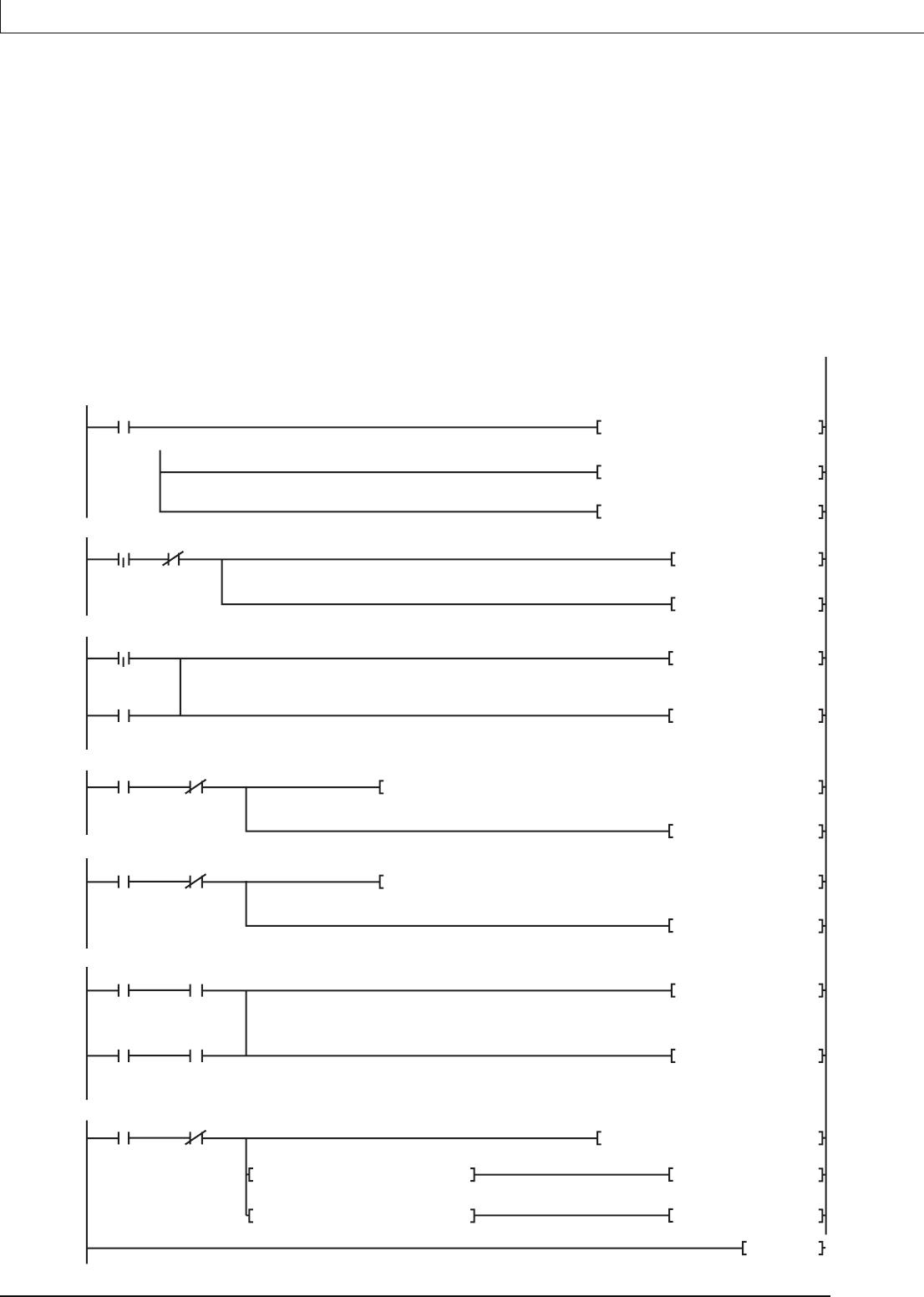

(b) Program example when the D(P).DDWR instructions are executed concurrently

The following shows a program example that writes ZR0 to ZR999 (1000 points) in CPU

No.1 to ZR0 to ZR999 in CPU No.2 with the D.DDWR instruction.

As shown on the program example, multiple CPU device write/read instructions can be

executed concurrently.

When reading/writing devices with the multiple CPU high-speed transmission dedicated

instructions concurrently, the more the total number of blocks in the multiple CPU high

speed transmission area (send area), the more the time taken to complete reading/

writing with the multiple CPU high-speed transmission dedicated instruction can be

shortened.

Program example when the D(P).DDWR instructions are executed concurrently

When the DDWR instruction is completed abnomally, the annunciator is turned on and data writing is stopped

158

M3 M4

Completion

device 1

Error

completion

device 1

SET F0

RST M0

During

writing

DDWR instruction

error display

M5 M6

Completion

device 2

Error

completion

device 2

Next data writing is requested at nomal completion of the second DDWR instruction

197

M5 M6

Completion

device 2

Error

completion

device 2

+ K200 Z2

< Z2 K1000

= Z2 K1000

PLS M7

Execution request of the

next DDWR instruction

RST M0

During writing

END

241

The maximum number of used blocks for multiple CPU high-speed

transmission dedicated instruction setting is set to CPU No.2

SM402

Turn-on for one

scan after RUN

MOV K7 SD797

Maximum number of

used blocks

(CPU No.2)

MOV K100 D1

Number of

write points 1

MOV K100 D3

Number of

write points 2

Data writing is started at the rise of the write command (X0)

X0 M0

Write

comma

During

writing

39

RST Z2

SET M0

During writing

First DDWR instruction, Second DDWR instruction

70

M0

During

writing

SET M1

During execution of

the DDWR instruction 1

SET M2

During execution of

the DDWR instruction 2

M7

Execution request of the next

DDWR instruction

The first DDWR instruction is executed

94

M1

During execution

of the DDWR

instruction 1

SM797

Number of used

blocks information

(CPU No.2)

D.DDWR H3E1 D0 ZR0Z2 ZR0Z2 M3

Completion

status 1

Write

destination

source write Completion

device 1

RST M1

During execution of the

DDWR instruction 1

The second DDWR instruction is executed

126

M2

During execution

of the DDWR

instruction 2

SM797

Number of used 3

blocks information

(CPU No.2)

D.DDWR H3E1 D2 ZR100Z2 ZR100Z2 M5

Completion

status 2

Write

destination

source write Completion

device 2

RST M2

During execution of the

DDWR instruction 2

0