10-9

7

10

7

7

7

7

7

7

10.1 Overview

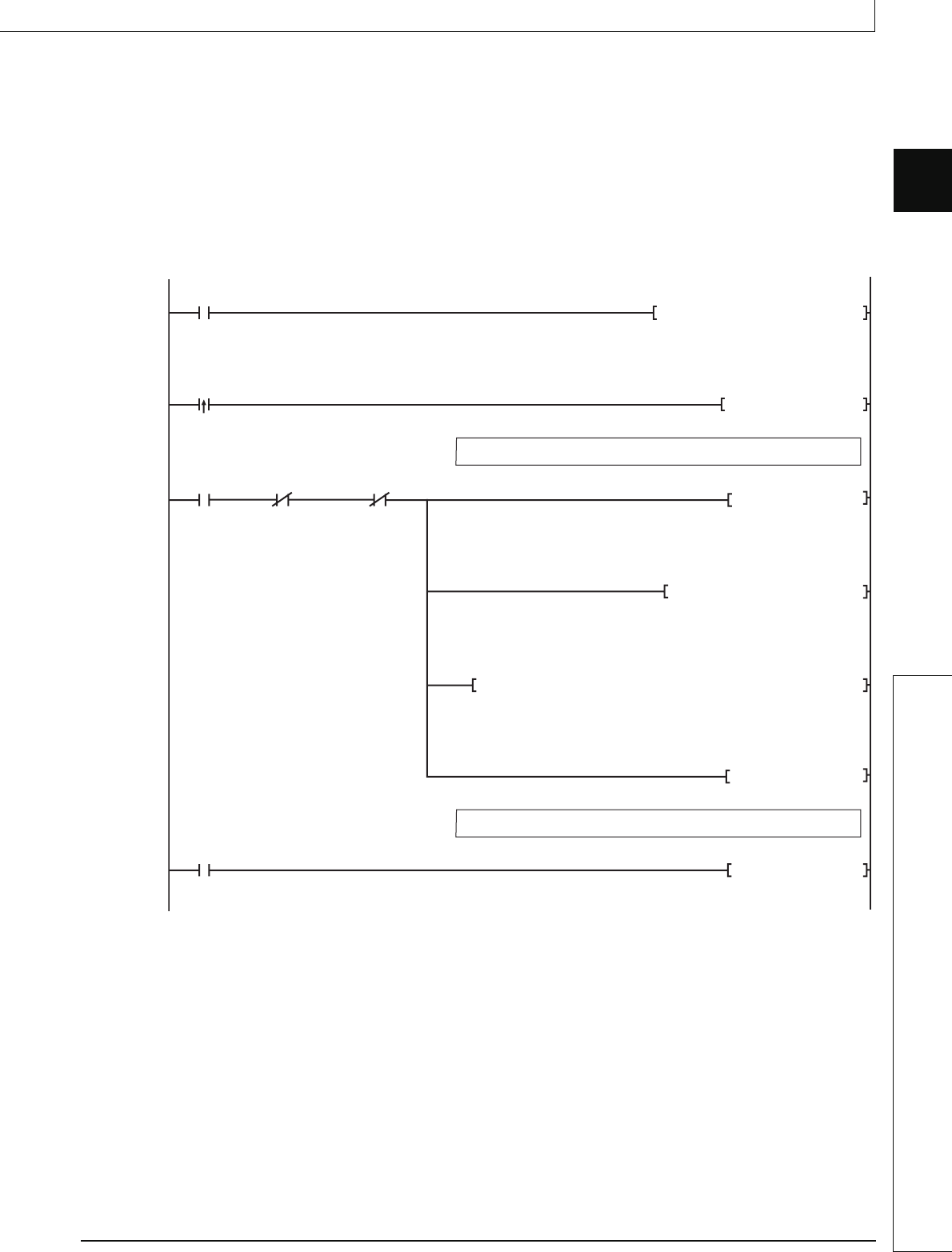

(8) Program example when the multiple CPU high-speed transmission dedicated instructions

are executed to CPU modules by turns

When the multiple CPU high-speed transmission dedicated instructions are executed to

Universal model QCPUs by turns, release an interlock to prevent the concurrent execution.

Use the cyclic transmission area device (from U3En¥G10000) as an interlock.

The following shows a program example when the multiple CPU high-speed transmission

dedicated instructions are executed at CPU No.s 1 and 2 by turns.

Program example when the multiple CPU high-speed transmission dedicated instruction is

executed at CPU No.1

SM402

Turn-on for one scan

after RUN

MOV K7 SD797

Maximum number

of used blocks

(CPU No.2)

X0

SET M0

During execution of the

DDWR instruction

Write command

U3E0

¥

G10000.0 is turned on while CPU No.1 is executing the DP.DDWR instruction.

M0 U3E1¥G10000.0 SM797

During execution

of the DDWR

instruction

CPU No.2 is

during execution

of the instruction

Number of used

blocks information

(CPU No.2)

SET G10000.0

U3E0¥

CPU No.1 is during

execution of the

instruction

MOV K100 D1

Number of

write points

DP.DDWR H3E1 D0 ZR100 ZR100 M1

Completion

status

Completion

device

RST M0

During execution of

the DDWR instruction

U3E0

¥

G10000.0 is turned on while CPU No.1 is executing the DP.DDWR instruction.

SET G10000.0

U3E0¥

CPU No.1 is during of

the instruction

M1

Completion device