5-50

MC,MCR

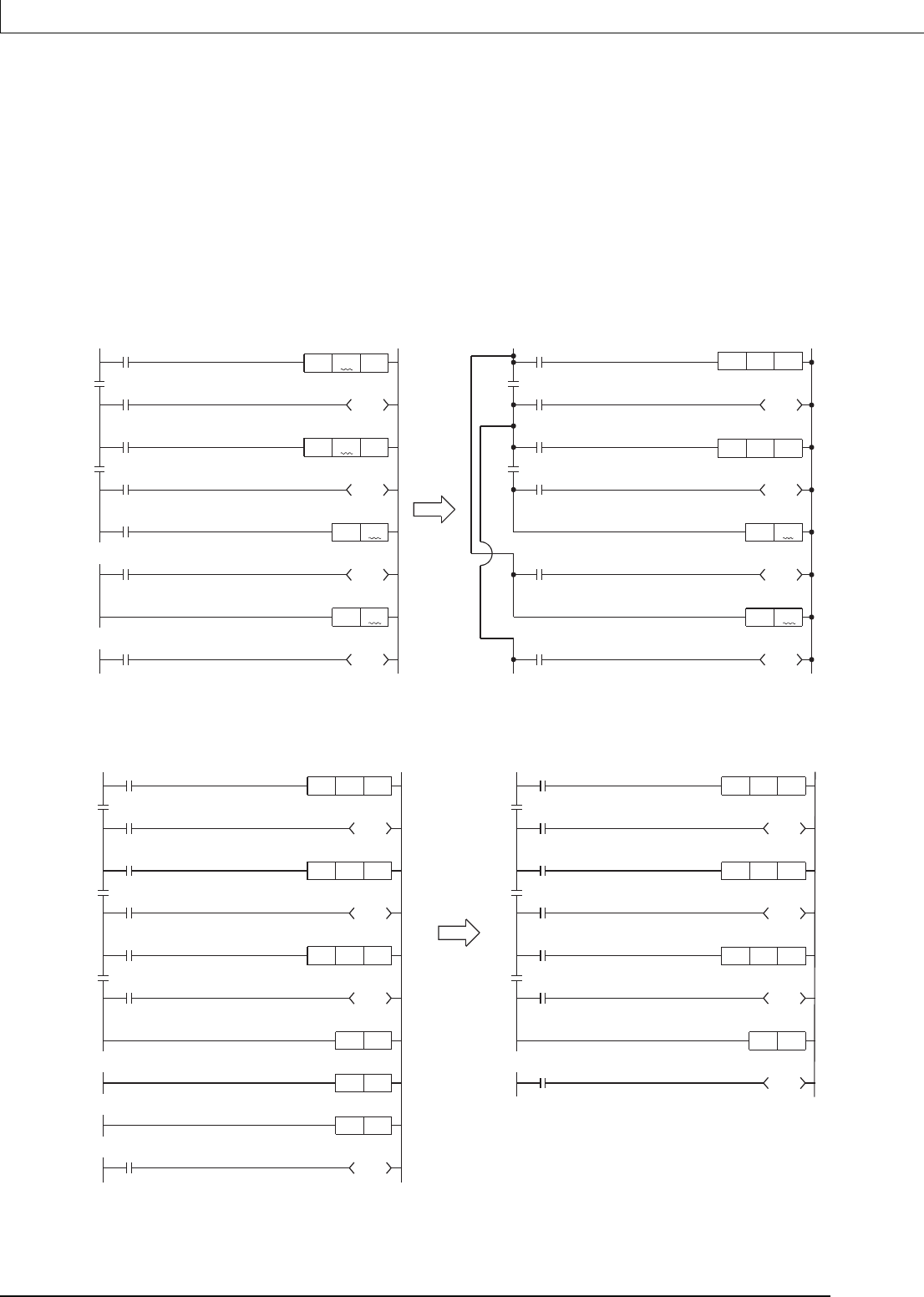

Cautions when Using Nesting Architecture

(1) Nesting can be used up to 15 times (N0 to N14)

When using nesting, nests should be inserted from the lower to higher nesting number (N)

with the MC instruction, and from the higher to the lower order with the MCR instruction.

If this order is reversed, there will be no nesting architecture, and the CPU module will not be

capable of performing correct operations. For example, if nesting is designated in the order

N1 to N0 by the MC instruction, and also designated in the N1 to N0 order by the MCR

instruction, the vertical bus will intersect and a correct master control ladder will not be

produced.

[Ladder as displayed in the GPP ladder mode] [Ladder as it actually operates]

(2) If the nesting architecture results in MCR instructions concentrated in one location, all

master controls can be terminated by use of just the lowest nesting number (N).

MC

N1

M15

MC N0M16

MCR

N0

N1

M15

N0M16

A

MCR

N1

MC

N1

M15

MC N0M16

MCR

N0

N1

M15

N0M16

A

B

MCR

N1

MC NO M15

MC N1

M16

MC N2M17

MCR

N2

MCR

N0

NO M15

N1M16

N2M17

X1

X2

X3

MCR

N1

MC NO M15

MC

N1

M16

MC

N2M17

MCR

N0

NOM15

N1M16

N2M17

X1

X2

X3