2-60

2.5.20 Multiple CPU dedicated instruction

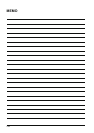

Table 2.37 Multipe CPU dedicated instruction

2.5.21 Multiple CPU high-speed transmission dedicated instruction

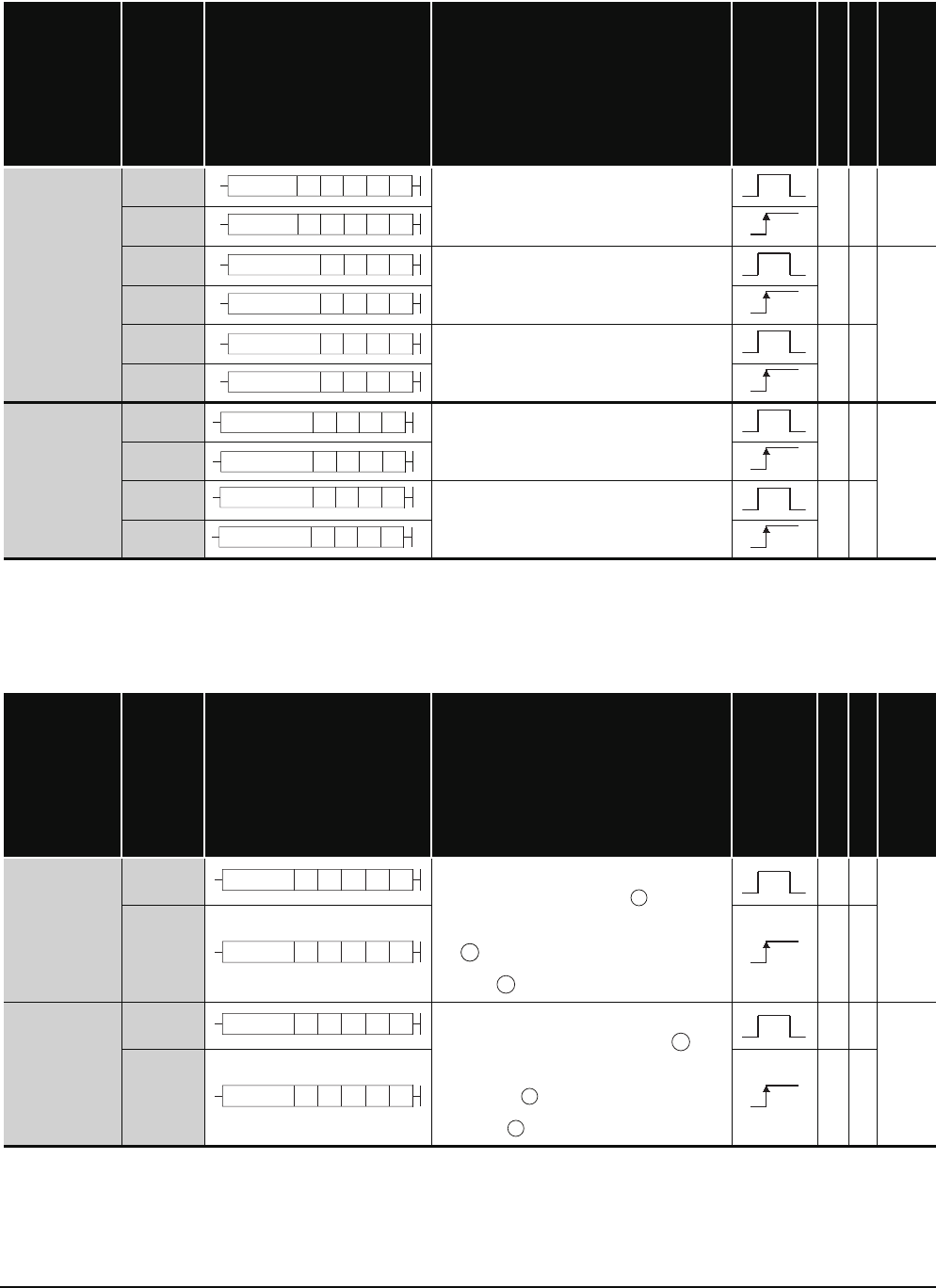

Table 2.40 Multiple CPU high-speed transmission dedicated instruction

Category

Instruction Symbol

Symbol Processing Details

Execution

Condition

Number of Basic Steps

Subset

See for Description

Write to host

CPU shared

memory

S. TO

• Writes device data of the host station to

the host CPU shared memory.

5- 9-4

SP. TO

TO

• Writes device data of the host station to

the host CPU shared memory.

5-

9-7

TOP

DTO

• Writes device data of the host station to

the host CPU shared memory in 32-bit

units.

5-

DTOP

Read from other

CPU shared

memory

FROM

• Reads device data from the other CPU

shared memories, and stores the data in

the host station.

5-

9-12

FROMP

DFRO

• Reads device data from the other CPU

shared memories in 32-bit units, and

stores the data in the host station.

5-

DFROP

Category

Instruction Symbol

Symbol Processing Details

Execution

Condition

Number of Basic Steps

Subset

See for Description

Writing Devices

to Another CPU

D.DDWR

In multiple CPU system, data stored in a

device specified by host CPU ( ) or later is

stored by the number of write points specified

by ( +1) into a device specified by another

CPU (n) ( ) or later

10 -

10-13

DP.DDWR

10 -

Reading Devices

from Another

CPU

D.DDRD

In multiple CPU system, data stored in a

device specified by another CPU (n) ( ) or

lrater is stored by the number of read points

specified by ( +1) into a device specified by

host CPU ( ) or late

10 -

10-17

DP.DDRD

10 -

Dn4n3n2S.TO n1

D

n4n3n2SP.TO

n1

n3n2

TO

n1

S

n3n2

TOP

n1

S

n3n2

DTO

n1

S

n3n2

DTOP

n1

S

n3Dn2n1FROM

n3Dn2n1FROMP

n3Dn2n1DFRO

n3Dn2n1DFROP

D2D1S2S1D.DDWR n

S2

D2

D1

D2D1S2S1

DP.DDWR

n

D2D1S2S1D.DDRD n

D1

S1

S2

D2D1S2S1

DP.DDRD

n