App-73

8

8

8

8

A

6

7

8

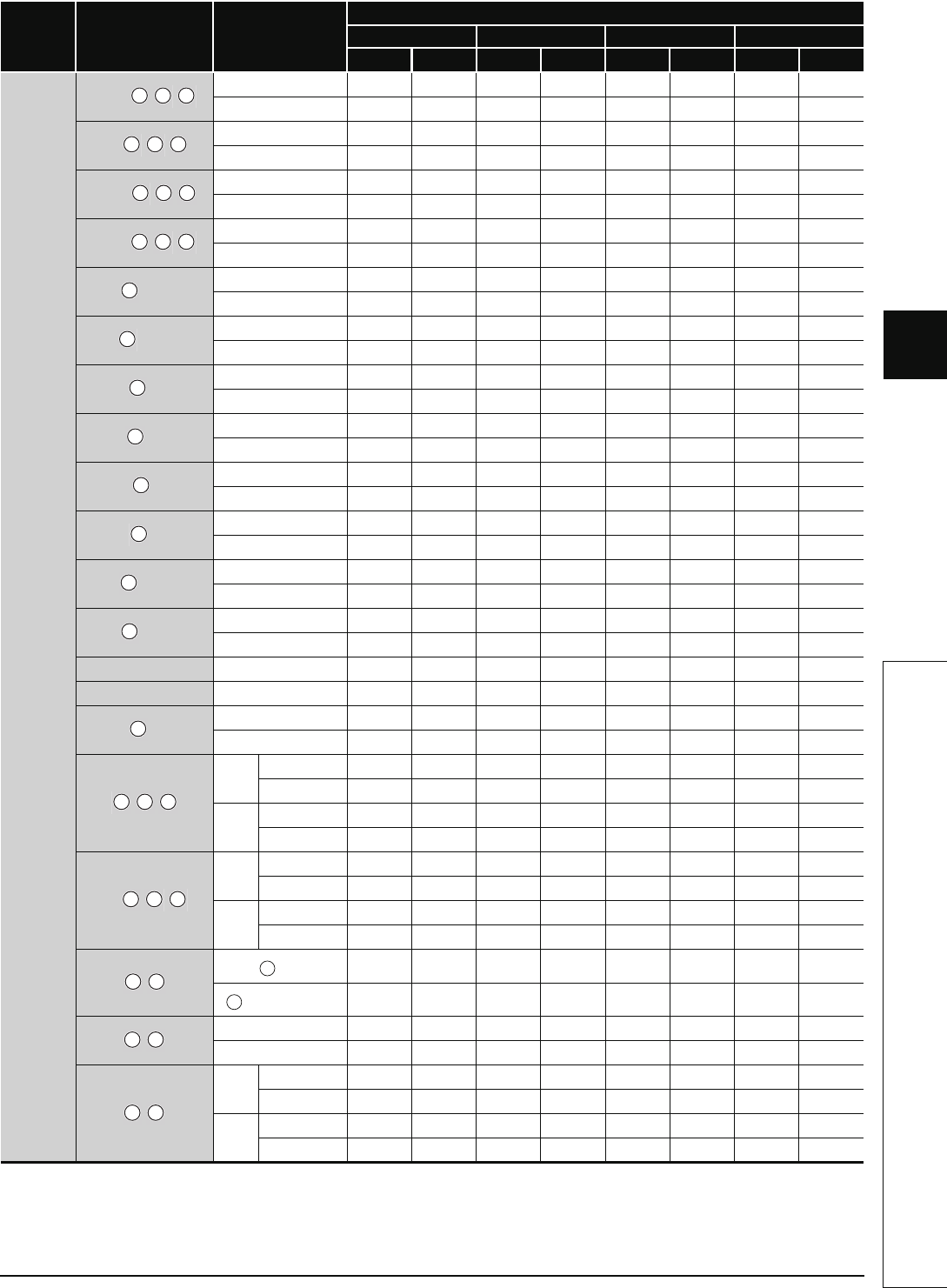

Appendix1 OPERATION PROCESSING TIME

Appendix 1.4 Operation Processing Time of Universal Model QCPU

Category Instruction Condition (Device)

Processing Time (µs)

Q00UJCPU Q00UCPU

Q01UCPU Q02UCPU

Min. Max. Min. Max. Min. Max. Min. Max.

Application

instruction

BKAND n

n = 1 13.600 28.500 13.600 28.500 13.600 28.500 12.100 20.100

n = 96 63.200 78.200 63.200 78.200 63.200 78.200 57.400 63.200

BKOR n

n = 1 13.500 28.500 13.500 28.500 13.500 28.500 7.700 13.200

n = 96 63.100 78.200 63.100 78.200 63.100 78.200 57.400 62.800

BKXOR n

n = 1 13.600 28.300 13.600 28.300 13.600 28.300 7.800 13.200

n = 96 63.100 78.000 63.100 78.000 63.100 78.000 57.300 62.800

BKXNR n

n = 1 13.500 28.300 13.500 28.300 13.500 28.300 7.800 14.100

n = 96 63.100 78.000 63.100 78.000 63.100 78.000 57.400 62.900

BSFR n

n = 1 5.050 21.100 5.050 21.100 5.050 21.100 3.700 6.300

n = 96 9.000 34.800 9.000 34.800 9.000 34.800 10.200 12.800

BSFL n

n = 1 4.800 19.100 4.800 19.100 4.800 19.100 4.500 8.900

n = 96 8.550 34.300 8.550 34.300 8.550 34.300 10.100 14.300

SFTBR n1 n2

n1 = 16 / n2 = 1 10.300 46.500 10.300 46.500 10.300 46.500 8.800 43.400

n1 = 16 / n2 = 15 10.300 46.400 10.300 46.400 10.300 46.400 8.750 43.400

SFTBL n1 n2

n1 = 16 / n2 = 1 10.500 49.800 10.500 49.800 10.500 49.800 8.050 45.100

n1 = 16 / n2 = 15 10.500 49.800 10.500 49.800 10.500 49.800 8.050 45.100

SFTWR n1 n2

n1 = 16 / n2 = 1 7.950 24.000 7.950 24.000 7.950 24.000 6.500 22.800

n1 = 16 / n2 = 15 7.950 24.100 7.950 24.100 7.950 24.100 6.500 22.800

SFTWL n1 n2

n1 = 16 / n2 = 1 8.700 23.600 8.700 23.600 8.700 23.600 7.350 23.600

n1 = 16 / n2 = 15 8.650 23.700 8.650 23.700 8.650 23.700 7.300 23.700

BSET n

n = 1 4.550 4.750 4.550 4.750 4.550 4.750 3.000 3.400

n = 15 4.550 4.750 4.550 4.750 4.550 4.750 3.000 3.500

BRST n

n = 1 4.600 4.750 4.600 4.750 4.600 4.750 3.000 3.400

n = 15 4.600 4.750 4.600 4.750 4.600 4.750 3.000 3.400

TEST

When executed 7.250 13.200 7.250 13.200 7.250 13.200 4.400 6.900

DTEST

When executed 6.950 12.900 6.950 12.900 6.950 12.900 4.500 7.000

BKRST n

n = 1 7.350 11.600 7.350 11.600 7.350 11.600 4.300 5.200

n = 96 10.100 22.600 10.100 22.600 10.100 22.600 6.500 13.200

SER n

n = 1

All match 6.650 6.800 6.650 6.800 6.650 6.800 5.000 5.300

None match 6.650 6.800 6.650 6.800 6.650 6.800 5.000 5.300

n =

96

All match 34.000 42.300 34.000 42.300 34.000 42.300 32.300 35.900

None match 34.000 42.300 34.000 42.300 34.000 42.300 32.400 35.900

DSER n

n = 1

All match 8.000 16.300 8.000 16.300 8.000 16.300 6.800 10.200

None match 8.000 16.300 8.000 16.300 8.000 16.300 6.800 10.200

n =

96

All match 54.100 62.600 54.100 62.600 54.100 62.600 52.800 56.300

None match 54.100 62.600 54.100 62.600 54.100 62.600 52.800 56.300

DSUM

= 0

4.100 4.200 4.100 4.200 4.100 4.200 3.700 4.100

= FFFFFFFF

H

4.100 4.200 4.100 4.200 4.100 4.200 3.800 4.100

DECO n

n = 2 8.850 23.000 8.850 23.000 8.850 23.000 6.000 16.400

n = 8 13.600 36.600 13.600 36.600 13.600 36.600 8.100 15.200

ENCO n

n = 2

M1 = ON 7.650 11.900 7.650 11.900 7.650 11.900 5.300 6.300

M4 = ON 7.500 11.700 7.500 11.700 7.500 11.700 5.200 6.200

n = 8

M1 = ON 14.600 27.800 14.600 27.800 14.600 27.800 10.400 17.900

M256 = ON 10.600 23.700 10.600 23.700 10.600 23.700 5.700 13.300

S1

S2

D

S1

S2

D

S1

S2

D

S1

S2

D

D

D

D

D

D

D

D

D

D

S1

S2

D

S1

S2

D

S D

S

S

S D

S D