9-7

TO(P), DTO(P)

9

7

7

7

7

7

7

7

9.1 Writing to the CPU Shared Memory of Host CPU

9.1.2 Writing to host station CPU shared memory (TO(P), DTO(P))

9.1.2 Writing to host station CPU shared memory (TO(P), DTO(P))

TO(P), DTO(P)

*2: The setting range varies depending on the auto refresh setting range of the multiple CPU high speed

transmission function.

Function

TO

(1) Writes device data of words to n3 to the CPU shared memory address specified by n2 of

the host CPU module or later address.

Q00CPU/Q01CPU whose first 5 digits of the serial No. is "04122" or higher

n1 : Head I/O number of the host CPU (BIN 16 bits)

• Basic model QCPU : 3E0

H

• Universal model QCPU: 3E0H to 3E3H

n2 : CPU shared memory address of the write destination host CPU (BIN 16 bits)

• Basic model QCPU : 192 to 511

• Universal model QCPU: 2048 to 4095, 10000 to 24335*

2

: Data to be written or head number of the devices where the data to be written is stored (BIN 16 bits)

n3 : Number of data blocks to be written (BIN 16 bits)

• Basic model QCPU : TO(P): 1 to 320, DTP(P) : 1 to 160

• Universal model QCPU: TO(P): 1 to 14336*

2

, DTP(P) : 1 to 7168*

2

Setting

Data

Internal Devices

R, ZR

J\

U\G

Zn

Constants

K, H

Other

U

Bit Word Bit Word

n1

n2 ––

–– ––

n3 ––

Universal

Redundant

Ver.

Basic

Process

High

performance

Command

Command

n3

n3

n1

n1

n2

n2

TO,DTO

TOP,DTOP

S

S

P

indicates an instruction symbol of TO/DTO.

S

S

S

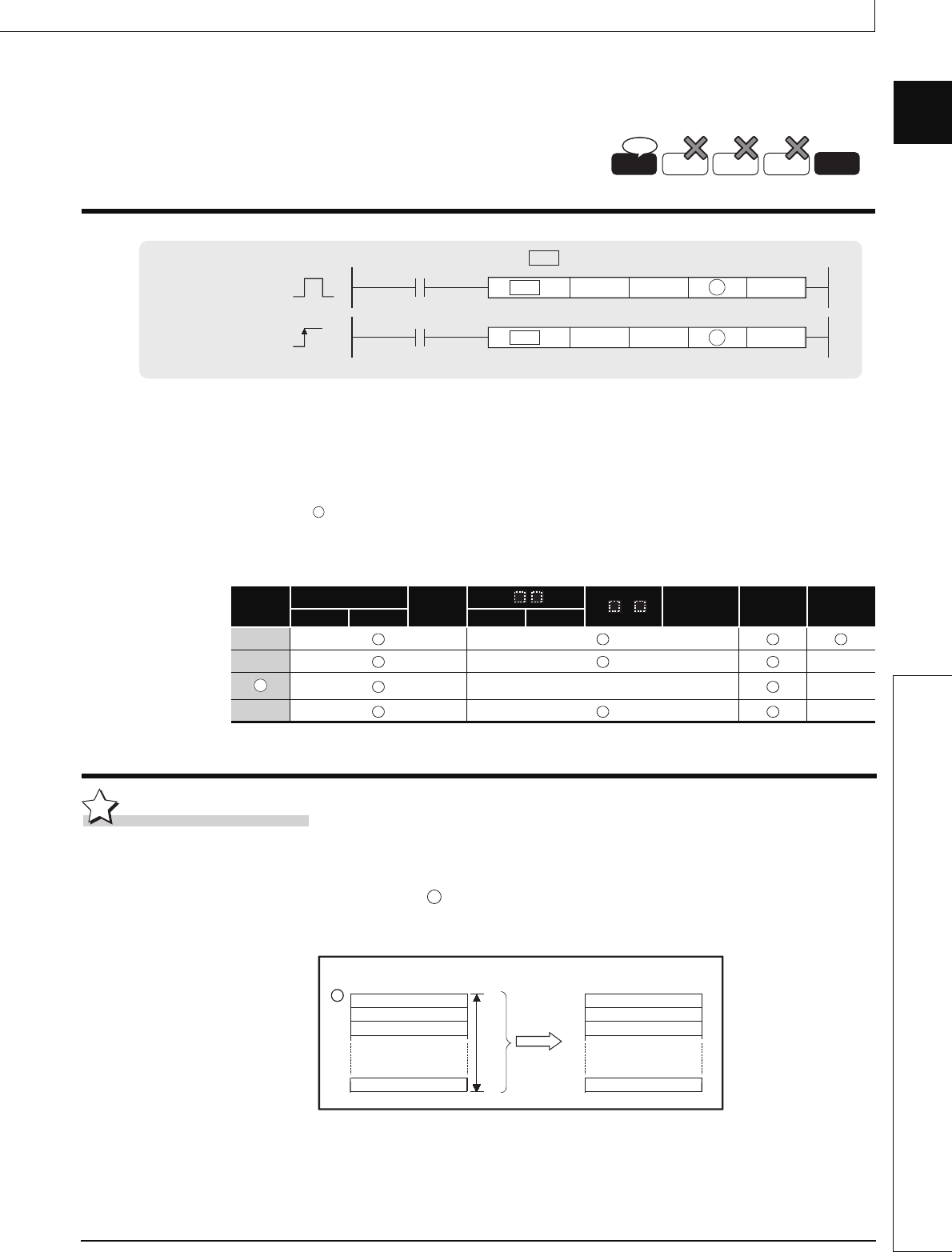

Device memory

Writes the

data of n3

words

Host CPU

n3

CPU shared memory

of host CPU (n1)

n2

S