App-111

8

8

8

8

A

6

7

8

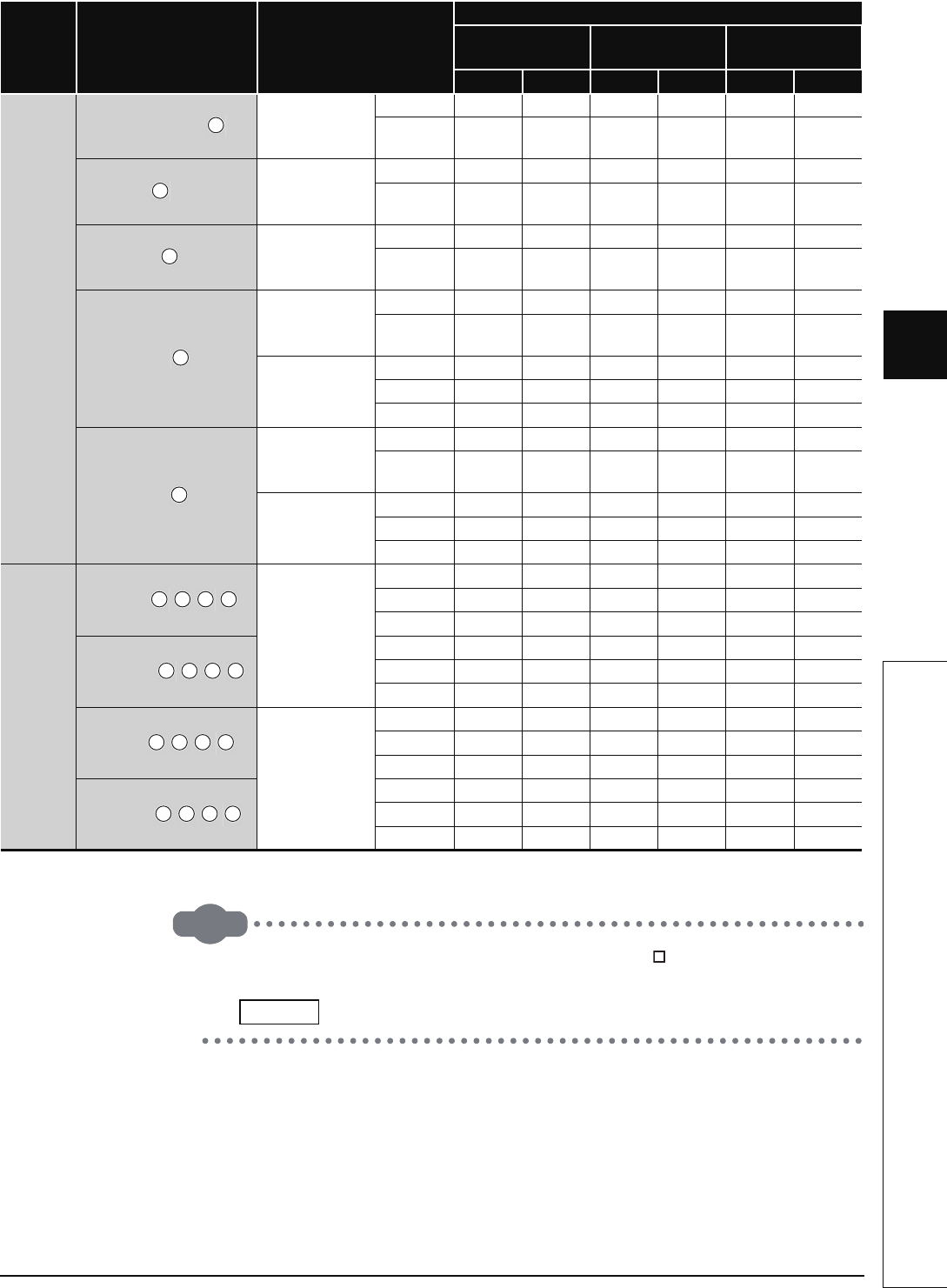

Appendix1 OPERATION PROCESSING TIME

Appendix 1.4 Operation Processing Time of Universal Model QCPU

Remark

the instructions for which a rise execution instruction ( P) is not specified, the

processing time is the same as an ON execution instruction.

WORDP instruction and TOP instruction

Category Instruction Condition (Device)

Processing Time (µs)

Q03UD(E)CPU

Q04/

Q06UD(E)HCPU

Q10/Q13/Q20/

Q26UD(E)HCPU

Min. Max. Min. Max. Min. Max.

Multiple

CPU

dedicated

instruction

S.TO n1 n2 n3 n4

Writing to host

CPU shared

memory

n4 = 1

34.700 34.900 33.500 34.400 33.500 34.400

n4 = 320

85.900 87.600 75.200 75.500 75.200 75.500

TO n1 n2 n3

Writing to host

CPU shared

memory

n3 = 1

4.700 23.800 5.200 23.300 5.200 23.300

n3 = 320

57.500 76.200 47.100 64.500 47.100 64.500

DTO n1 n2 n3

Writing to host

CPU shared

memory

n3 = 1

5.300 23.800 5.800 23.300 5.800 23.300

n3 = 320

111.300 128.400 91.500 108.500 91.500 108.500

FROM n1 n2 n3

Reading from

host CPU shared

memory

n3 = 1

5.000 23.800 4.300 23.300 4.300 23.300

n3 = 320

51.400 65.600 44.400 60.700 44.400 60.700

Reading from

other CPU

shared memory

n3 = 1

11.600 17.700 10.600 13.900 10.600 13.900

n3 = 320

142.000 160.000 142.000 149.000 142.000 149.000

n3 = 1000

431.000 463.000 422.000 448.000 422.000 448.000

DFRO n1 n2 n3

Reading from

host CPU shared

memory

n3 = 1

5.200 23.800 5.600 23.300 5.600 23.300

n3 = 320

96.400 113.200 83.600 100.800 83.600 100.800

Reading from

other CPU

shared memory

n3 = 1

12.900 20.800 12.200 17.100 12.200 17.100

n3 = 320

277.000 299.000 274.000 291.000 274.000 291.000

n3 = 1000

838.000 860.000 835.000 857.000 835.000 857.000

Multiple

CPU high-

speed

transmis-

sion dedi-

cated

instruction

D.DDWR n

Writes devices to

another CPU.

n=1

34.700 34.900 33.500 34.400 33.500 34.400

n=16

85.900 87.600 75.200 75.500 75.200 75.500

n=96

5.600 10.200 3.300 9.900 3.300 9.900

DP.DDWR n

n=1

36.700 42.400 34.300 39.200 34.300 39.200

n=16

5.000 12.100 3.100 10.500 3.100 10.500

n=96

59.100 66.800 55.300 65.100 55.300 65.100

D.DDRD n

Reads devices

from another

CPU.

n=1

3.300 12.700 2.400 9.600 2.400 9.600

n=16

50.900 64.400 45.200 48.200 45.200 48.200

n=96

11.600 17.700 10.600 13.900 10.600 13.900

DP.DDRD n

n=1

142.000 160.000 142.000 149.000 142.000 149.000

n=16

431.000 463.000 422.000 448.000 422.000 448.000

n=96

6.700 12.600 2.800 9.900 2.800 9.900

D

S

S

D

D

S1

S2

D1

D2

S1

S2

D1

D2

S1

S2

D1

D2

S1

S2

D1

D2

Example