App-133

8

8

8

8

A

8

7

8

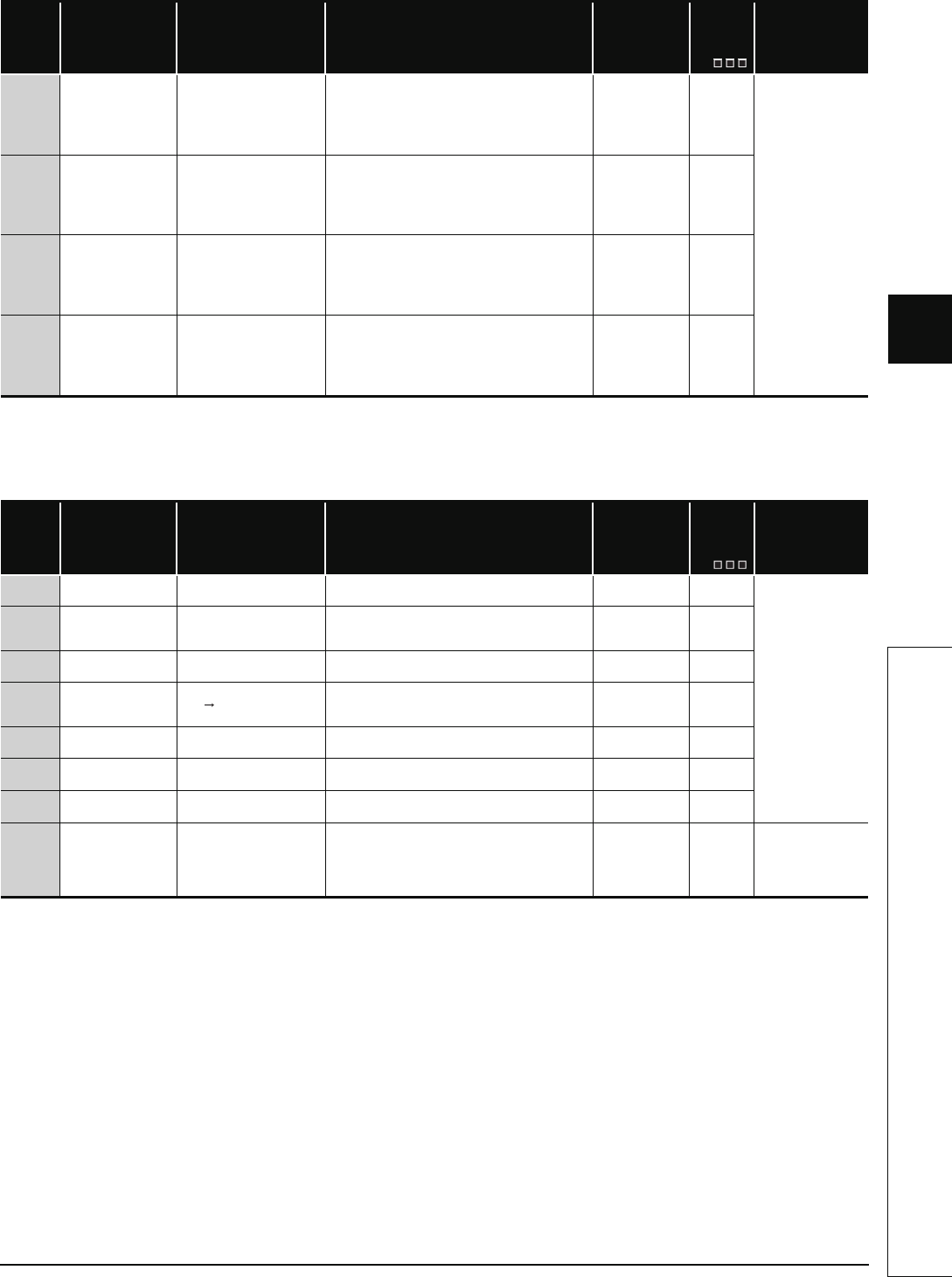

Appendix 3 SPECIAL RELAY LIST

*7: The Universal model QCPU except the Q00UJCPU, Q00UCPU, Q01UCPU, and Q02UCPU.

(8) Debug

*1: The Universal model QCPU except the Q00UJCPU.

TableApp.3.8 Special relay

Number Name Meaning Explanation

Set by

(When Set)

Corres-

ponding

ACPU

M9

Corresponding

CPU

SM796

Block information

using multiple CPU

high-speed

transmission

dedicated instruction

(for CPU No.1)

OFF : Block is secured

ON : Block set by SD796

cannot be secured

• Turns ON when the number of the remaining blocks

of the dedicated instruction transmission area used

for the multiple CPU high-speed transmission

dedicated instruction(target CPU= CPU No.1) is less

than the number of blocks specified by SD796.

Turns ON at instruction execution. Turns OFF when

the empty area exists at END processing.

S (When

instruction/END

processing

executed)

New

QnU

*7

SM797

Block information

using multiple CPU

high-speed

transmission

dedicated instruction

(for CPU No.2)

OFF : Block is secured

ON : Block set by SD797

cannot be secured

• Turns ON when the number of the remaining blocks

of the dedicated instruction transmission area used

for the multiple CPU high-speed transmission

dedicated instruction (target CPU= CPU No.2) is less

than the number of blocks specified by SD797.

Turns ON at instruction execution. Turns OFF when

the empty area exists at END processing.

S (When

instruction/END

processing

executed)

New

SM798

Block information

using multiple CPU

high-speed

transmission

dedicated instruction

(for CPU No.3)

OFF : Block is secured

ON : Block set by SD798

cannot be secured

• Turns ON when the number of the remaining blocks

of the dedicated instruction transmission area used

for the multiple CPU high-speed transmission

dedicated instruction (target CPU= CPU No.3) is less

than the number of blocks specified by SD798.

Turns ON at instruction execution. Turns OFF when

the empty area exists at END processing.

S (When

instruction/END

processing

executed)

New

SM799

Block information

using multiple CPU

high-speed

transmission

dedicated instruction

(for CPU No.4)

OFF : Block is secured

ON : Block set by SD799

cannot be secured

• Turns ON when the number of the remaining blocks

of the dedicated instruction transmission area used

for the multiple CPU high-speed transmission

dedicated instruction(target CPU= CPU No.4) is less

than the number of blocks specified by SD799.

Turns ON at instruction execution. Turns OFF when

the empty area exists at END processing.

S (When

instruction/END

processing

executed)

New

TableApp.3.9 Special relay

Number Name Meaning Explanation

Set by

(When Set)

Corres-

ponding

ACPU

M9

Corresponding

CPU

SM800 Trace preparation

OFF : Not ready

ON : Ready

• Switches ON when the trace preparation is

completed

S (Status change) New

Qn(H)

QnPH

QnPRH

QnU

*1

SM801 Trace start

OFF : Suspend

ON : Start

• Trace is started when this relay switches ON.

• Trace is suspended when this relay switches OFF.

(All related special Ms switches OFF.)

U M9047

SM802

Trace execution in

progress

OFF : Suspend

ON : Start

• Switches ON during execution of trace. S (Status change) M9046

SM803 Trace trigger

OFF ON: Start

• Trace is triggered when this relay switches from OFF

to ON. (Identical to TRACE instruction execution

status)

U M9044

SM804 After trace trigger

OFF : Not after trigger

ON : After trigger

• Switches ON after trace is triggered. S (Status change) New

SM805 Trace completed

OFF : Not completed

ON : End

• Switches ON at completion of trace S (Status change) M9043

SM826 Trace error

OFF : Normal

ON : Errors

• Switches ON if error occurs during execution of trace S (Status change) New

SM829

Forced registration

specification of trace

setting

ON : Forced registration

enabled

OFF : Forced registration

disabled

• Even when the trace condition or the trigger

condition is established, the sampling trace setting

can be set to the CPU module by turning SM829 ON

and registering the sampling trace setting by GX

Developer.

UNew

QnU

*1