SPI-4.2 Lite v4.3 User Guide www.xilinx.com 111

UG181 June 27, 2008

R

Chapter 6

Special Design Considerations

This chapter describes several design considerations to consider when designing with the

Xilinx SPI-4.2 Lite core:

• Clocking implementations

• Multiple core implementations

Sink Clocking Options

The Sink core supports two clocking implementations: embedded clocking and user

clocking. The embedded clocking configuration provides a complete solution with the

clock circuitry embedded within the Sink core. The user clocking configuration allows the

clocking scheme to be implemented external to the Sink core. This enables the user to craft

a custom clocking solution. The embedded and user clocking configurations are described

in detail below.

Embedded Clocking

The embedded clocking configuration contains the clocking logic internal to the core. The

embedded clocking option always uses global clocking distribution. The implementation

of the embedded clocking option is illustrated in Figure 6-1. Because all global clocks are

implemented differentially, this clocking scheme also minimizes duty-cycle distortion.

Note that the inverter used to generate RDClk180_GP will be absorbed into the DDR flip-

flops. Table 6-1 provides the clocking resource count for the embedded clocking

configuration.

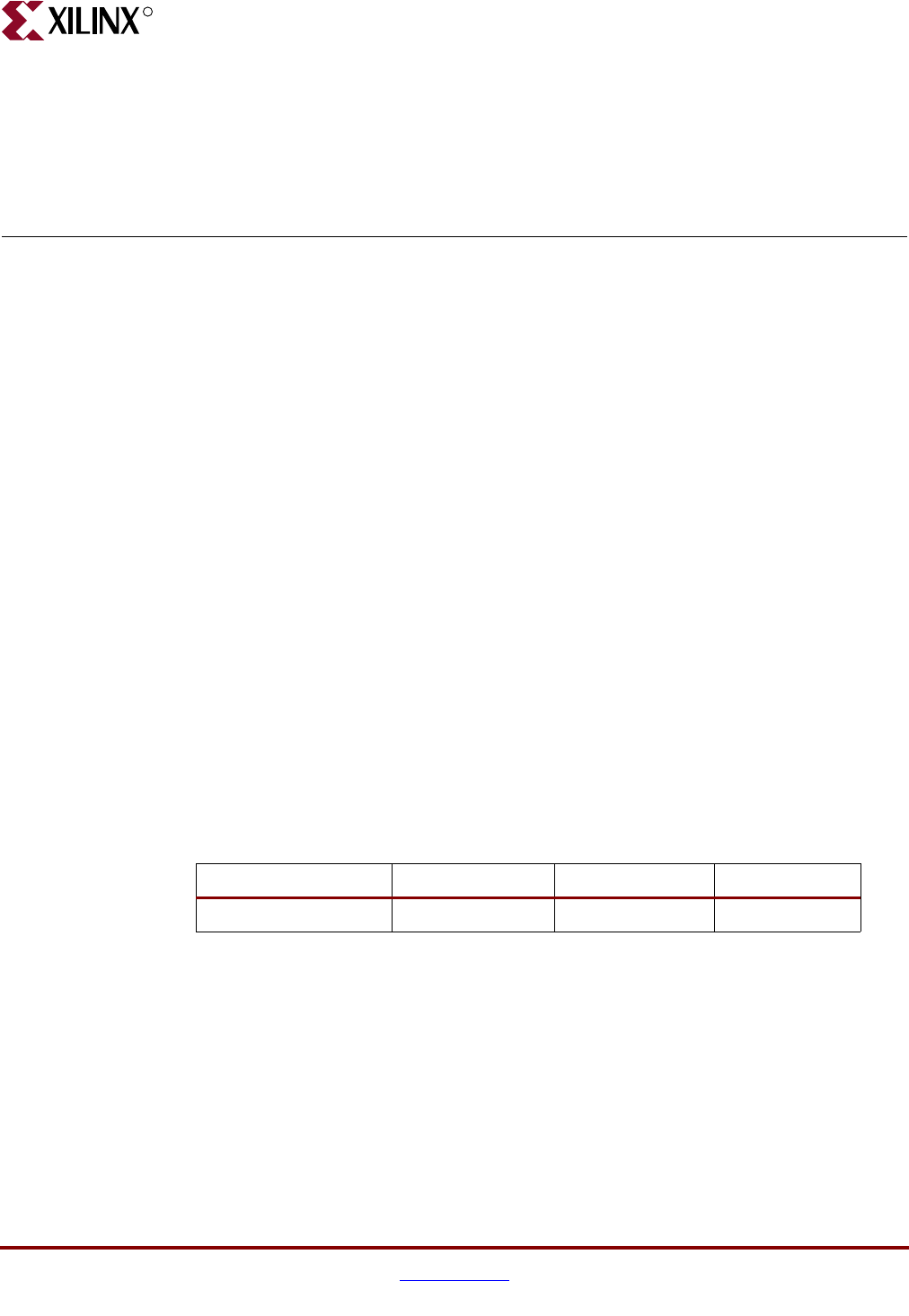

Table 6-1: Sink Core Embedded Clocking Resources

Clocking Distribution BUFR BUFG DCM

Global Clocking 0 1 1