116 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 6: Special Design Considerations

R

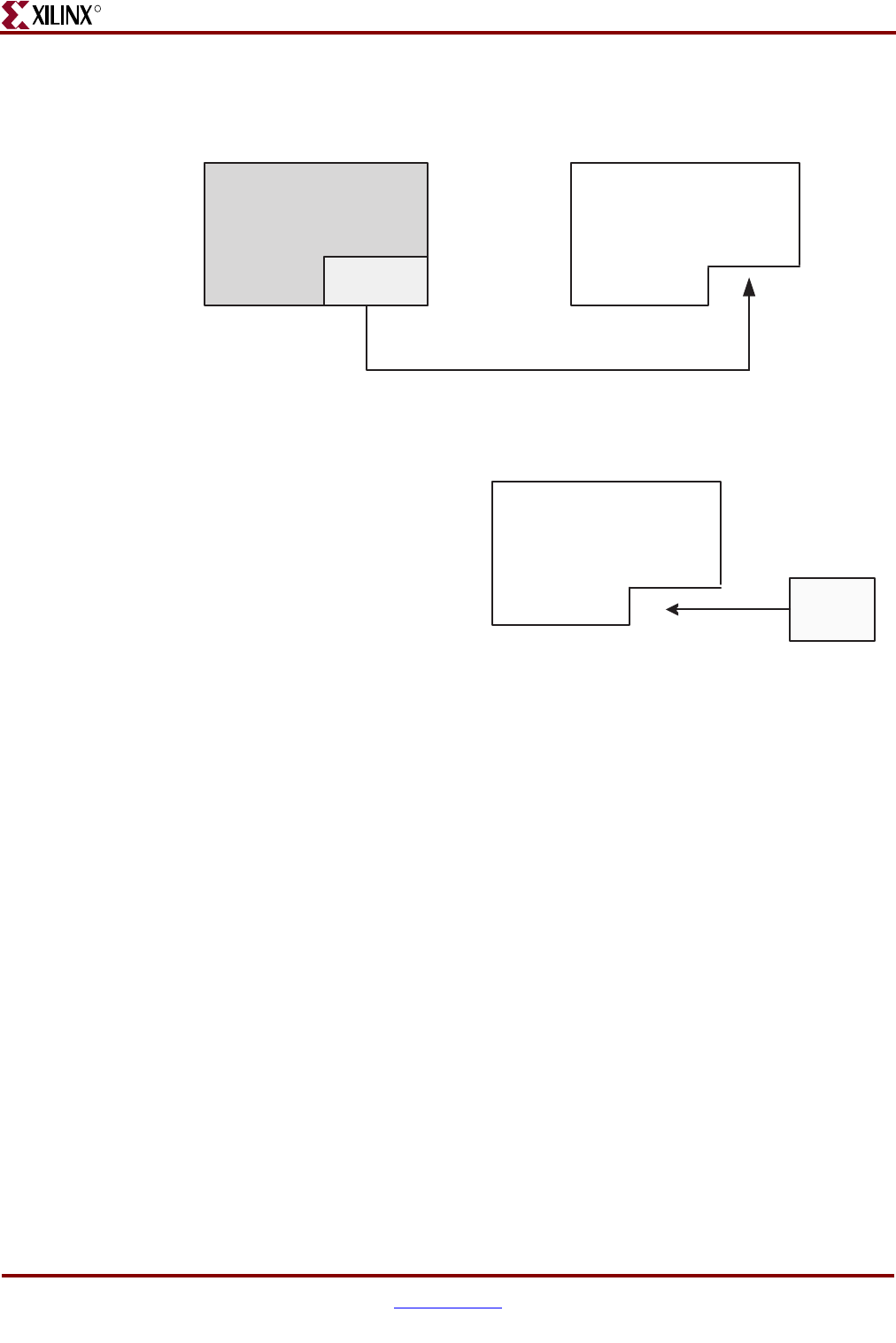

cores. An example of using the Slave core to either share clock resources between Source

cores or to implement a custom clocking solution is shown in Figure 6-5.

Master and slave clocking configurations are described in the following sections.

Master Clocking

The master clocking configuration contains the clocking logic internal to the core. For all

architectures other than Virtex-4 and Virtex-5 FPGAs, user clocking can only be

implemented using global clocking resources. When targeting the Virtex-4 or Virtex-5

device architectures, embedded clocking can be configured in one of two ways:

Global Clocking

This implementation uses the DCM and global clock routing to generate a full-rate clock

(SysClk0_GP), an inverted full-rate clock (SysClk180_GP), and the quarter-rate clock

(TSClk_GP). The global clocking implementation for SysClk is illustrated in Figure 6-6

and the global clocking implementation for TSClk is illustrated Figure 6-7. Note that the

inverter used to generate the SysClk180 clock will be absorbed into the DDR flops.

Figure 6-5: Source Clocking: Master and Slave Implementation

Source clocks shared between multiple cores

Custom

Clocking

Module

Source Core:

Slave Clocking

Source Core:

Slave Clocking

Source Core:

Master Clocking

Clocking

Module