SPI-4.2 Lite v4.3 User Guide www.xilinx.com 81

UG181 June 27, 2008

Source Core

R

Transmitting Training Patterns

Training patterns are transmitted at startup (after reset) until the core acquires

synchronization on the FIFO Status Channel. Subsequently, if the parameter DataMaxT or

AlphaData are not zero, the core will transmit AlphaData training patterns at least every

DataMaxT cycles.

The core continuously monitors the number of data cycles since the transmission of the last

training pattern. Once a DataMaxT interval of SPI-4.2 bus cycles has completed, the

current transfer is terminated on the next burst boundary, and training patterns will be

transmitted on the SPI-4.2 bus (AlphaData number of times). Once the training patterns

have completed, the SPI-4.2 Lite core will resume transmission of data on the data bus.

The control signal TrainingRequest (see Table 2-11) is provided for you to request that

training patterns be sent out of the Source SPI-4.2 interface. When the TrainingRequest

signal is asserted, the transmission of data is halted on the next burst boundary and

training patterns are transmitted on the SPI-4.2 Interface.

If the static configuration signal AlphaData[7:0] (see Table 2-15) is set to zero, and the

TrainingRequest signal is asserted, the Source core will transmit a complete training

pattern sequence. The core will continue to transmit training patterns until

TrainingRequest is deasserted. When it is deasserted, the core will halt transmission of

training patterns after the current sequence is complete.

If the static configuration signal AlphaData[5:0] is set to a non zero value, the Source

core sends the number of training patterns defined by AlphaData every time it detects a

rising edge on the TrainingRequest signal.

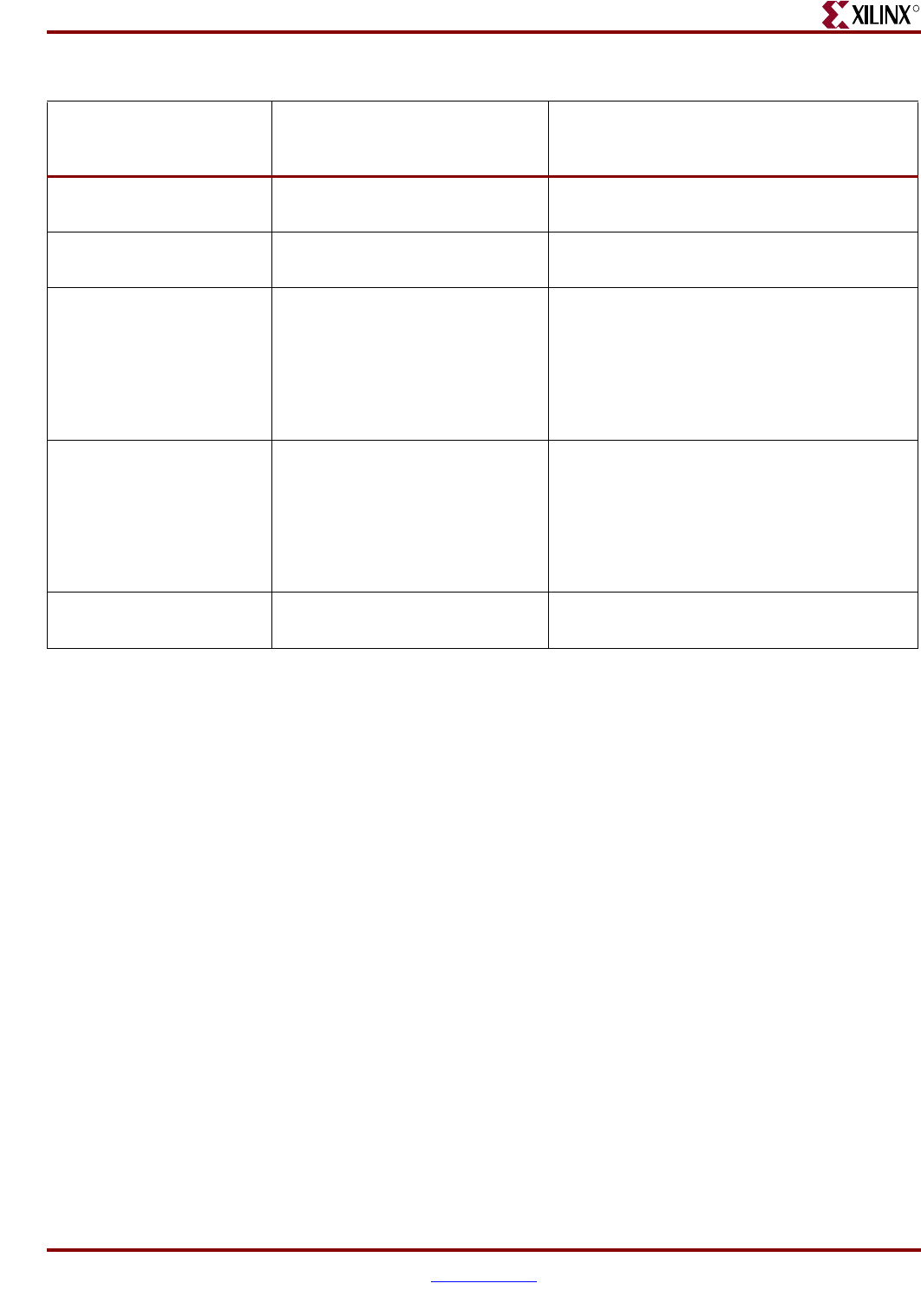

Table 4-8: SPI-4.2 Control Word Mapping to 64-bit User Interface

Control Word

Associated SPI-4.2 Lite Control

Word bits on TDat (Qualified by

TCtl=1)

Associated Source FIFO Signal(s)

Start of Packet (SOP) TDat[15] =1, TDat[12]=1,

TDat[11:4] <== SrcFFAddr[7:0]

SrcFFSOP, SrcFFAddr[7:0]

New Burst (address change

without SOP)

TDat[15] = 1, TDat[12] = 0,

TDat[11:4] <== SrcFFAddr[7:0]

SrcFFAddr[7:0]

End of Packet

(EOP, even bytes valid)

TDat[14:13] = 10 SrcFFEOP, SrcFFMOD[2:0]

When TDat[14:13] = 10:

MOD = 000 if data bits 63-0 have valid data

MOD =110 if data bits 63-16 have valid data

MOD =100 if data bits 63-32 have valid data

MOD = 010 if data bits 63-48 have valid data

End of Packet

(EOP, odd bytes valid)

TDat[14:13] = 11 SrcFFWEOP & SrcFFWMod[2:0]

When TDat[14:13] = 11:

MOD = 111 if data bits 63-8 have valid data

MOD = 101 if data bits 63-24 have valid data

MOD = 011 if data bits 63-40 have valid data

MOD = 001 if data bits 63-56 have valid data

End of Packet

(EOP, abort, error condition)

TDat[14:13] = 01 SrcFFErr, SrcFFEOP,

SrcFFMOD[2:0]