SPI-4.2 Lite v4.3 User Guide www.xilinx.com 115

UG181 June 27, 2008

Source Clocking Options

R

Source Clocking Options

The Source core supports two clocking implementations: master clocking and slave

clocking. The master clocking configuration provides a complete solution with the clock

circuitry embedded within the Source core. The slave clocking configuration allows the

clocking scheme to be implemented external to the Source core. This enables the user to

craft a custom clocking solution or to share the full-rate system clock with multiple Source

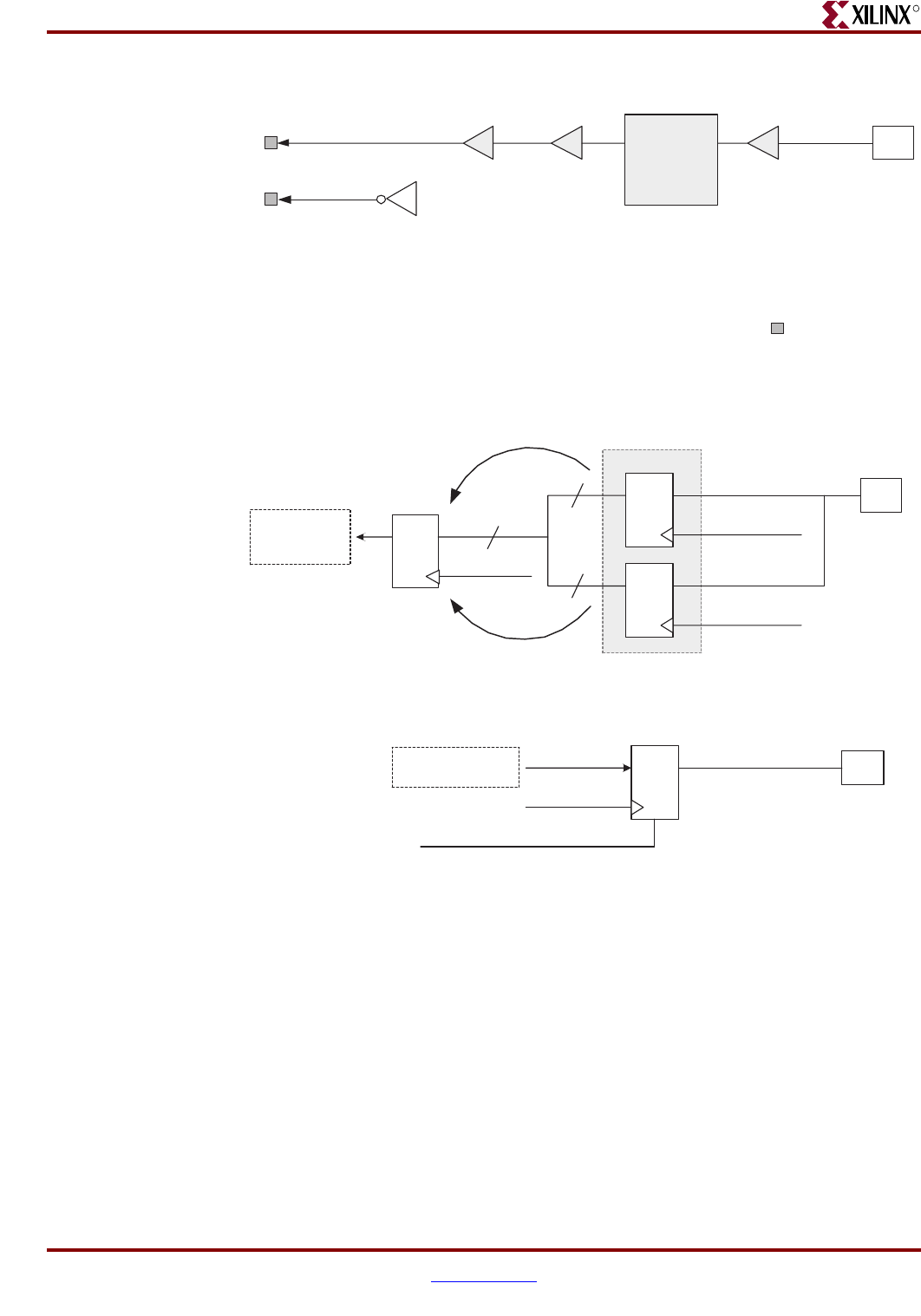

Figure 6-4: Sink User Clocking: Regional Clocking

RDClk0_USER

IOB

RDClk

Denotes I/O on User Interface

RDat[15:0] & RCtl

IOB

Q D

Q D

RDClk0_GP

RDClk180_GP

IOB DDR Flops

RDClk0_GP

Q D

Sink Internal

Data & Control

Bus

RDClk0_GP

D Q

EN

Enable at ¼ (or 1/8) PL4 Rx data rate

IOB

RStat[1:0] & RSClkInternal Bus

RStat[1:0] & RSClk

100 MHz

100 MHz

100 MHz

100 MHz

100 MHz

100 MHz

25 MHz

32

16

16

100 MHz Path

200 MHz Path

RDClk180_USER

BUFIOBUFR IBUFDS

O I

IDELAY