SPI-4.2 Lite v4.3 User Guide www.xilinx.com 35

UG181 June 27, 2008

Source Core Interfaces

R

Source FIFO Interface

The Source FIFO Interface signals allow you to write data into the FIFO to be transmitted

on the SPI-4.2 Interface. Table 2-12 defines the Source FIFO signals.

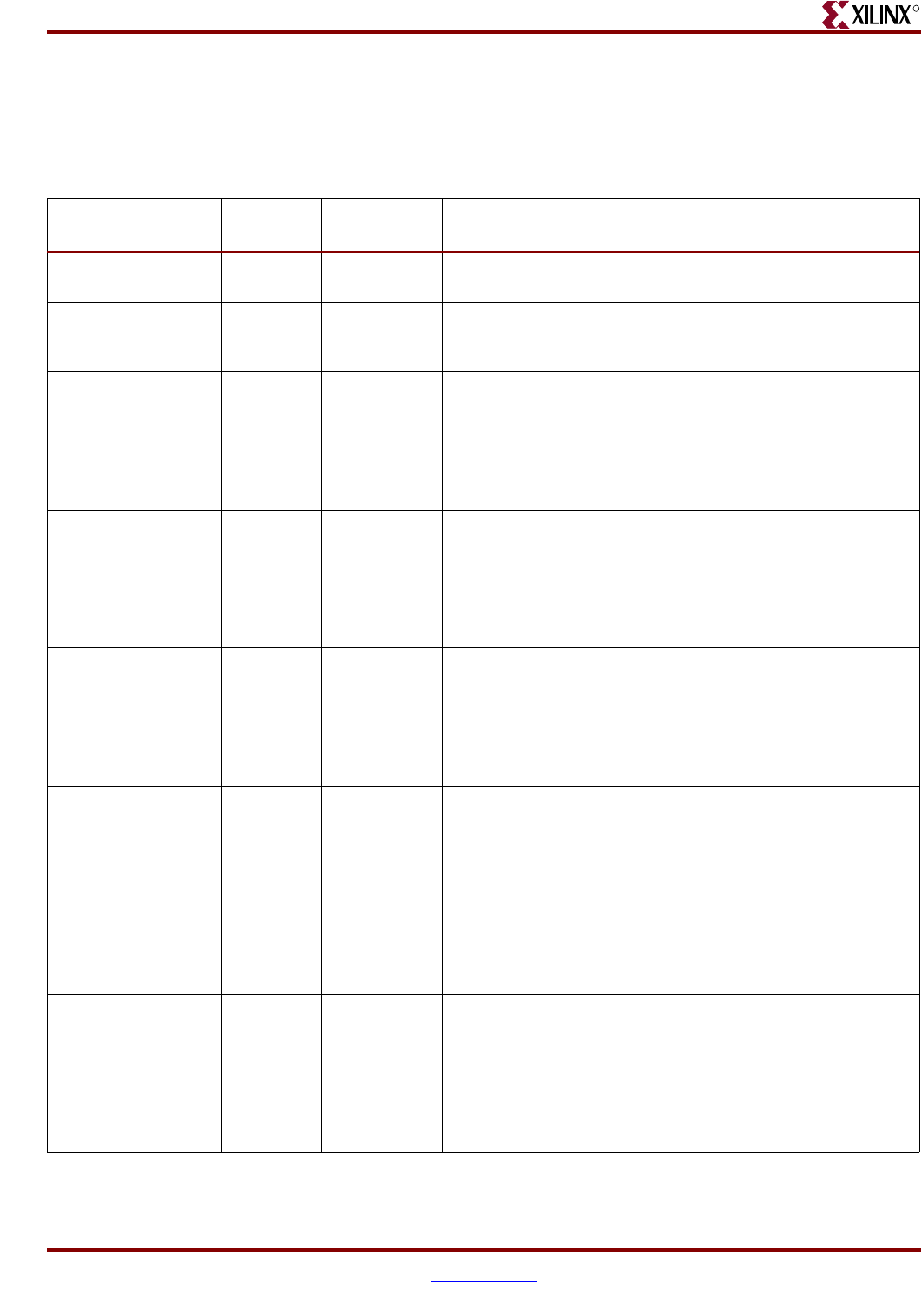

Table 2-12: S

ource FIFO Signals

Name Direction

Clock

Domain

Description

SrcFFClk Input n/a Source FIFO Clock: All Source FIFO Interface signals are

synchronous to the rising edge of this clock.

SrcFFWrEn_n Input SrcFFClk Source FIFO Write-Enable: When asserted (active low) at the rising

edge of SrcFFClk, data and packet information is written into the

FIFO.

SrcFFAddr[7:0] Input SrcFFClk Source FIFO Channel Address: Channel number associated with

the data on SrcFFData.

SrcFFData[31:0]

or

SrcFFData[63:0]

Input SrcFFClk Source FIFO Data: The Source FIFO data bus. Bit 0 is the LSB. The

core can be configured to have a 32-bit or a 64-bit interface. The 64-

bit interface enables you to run at half the clock rate required for a

32-bit interface.

SrcFFMod[1:0]

or

SrcFFMod[2:0]

Input SrcFFClk Source FIFO Modulo: This signal indicates which bytes on the

SrcFFData bus are valid when the SrcFFEOP or SrcFFErr signal is

asserted. When SrcFFEOP is deasserted, SrcFFMod should always

be zero.

SrcFFMod[1:0] is used with a 32-bit interface.

SrcFFMod[2:0] is used with a 64-bit interface.

SrcFFSOP Input SrcFFClk Source FIFO Start of Packet: When asserted (active high), this

signal indicates that the start of a packet is being written into the

Source FIFO.

SrcFFEOP Input SrcFFClk Source FIFO End of Packet: When asserted (active high), this signal

indicates that the end of a packet is being written into the Source

FIFO. May be concurrent with SrcFFSOP.

SrcFFErr Input SrcFFClk Source FIFO Error: When asserted (active high) simultaneously

with the SrcFFEOP flag, the current packet written into the FIFO

contains an error. This causes an EOP abort to be sent on the SPI-4.2

Interface.

SrcFFErr can be used in combination with SrcFFEOP to insert

erroneous DIP-4 values for testing purposes. When SrcFFErr is

asserted and SrcFFEOP is not asserted, the core inserts an EOP (1 or

2 bytes depending on the SrcFFMod value) with an erroneous DIP-

4 value. The erroneous DIP4 value is an inversion of the correctly

calculated value.

SrcFFAlmostFull_n Output SrcFFClk Source FIFO Almost Full: When asserted (active low), this signal

indicates that the FIFO is approaching full, and no more data

should be written.

SrcFFOverflow_n Output SrcFFClk Source FIFO Overflow: When asserted (active low), this signal

indicates that the FIFO has overflowed and is in an error condition.

No more data can be written until it is deasserted. SrcFFWrEn_n is

ignored if SrcFFOverflow_n is asserted.