34 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 2: Core Architecture

R

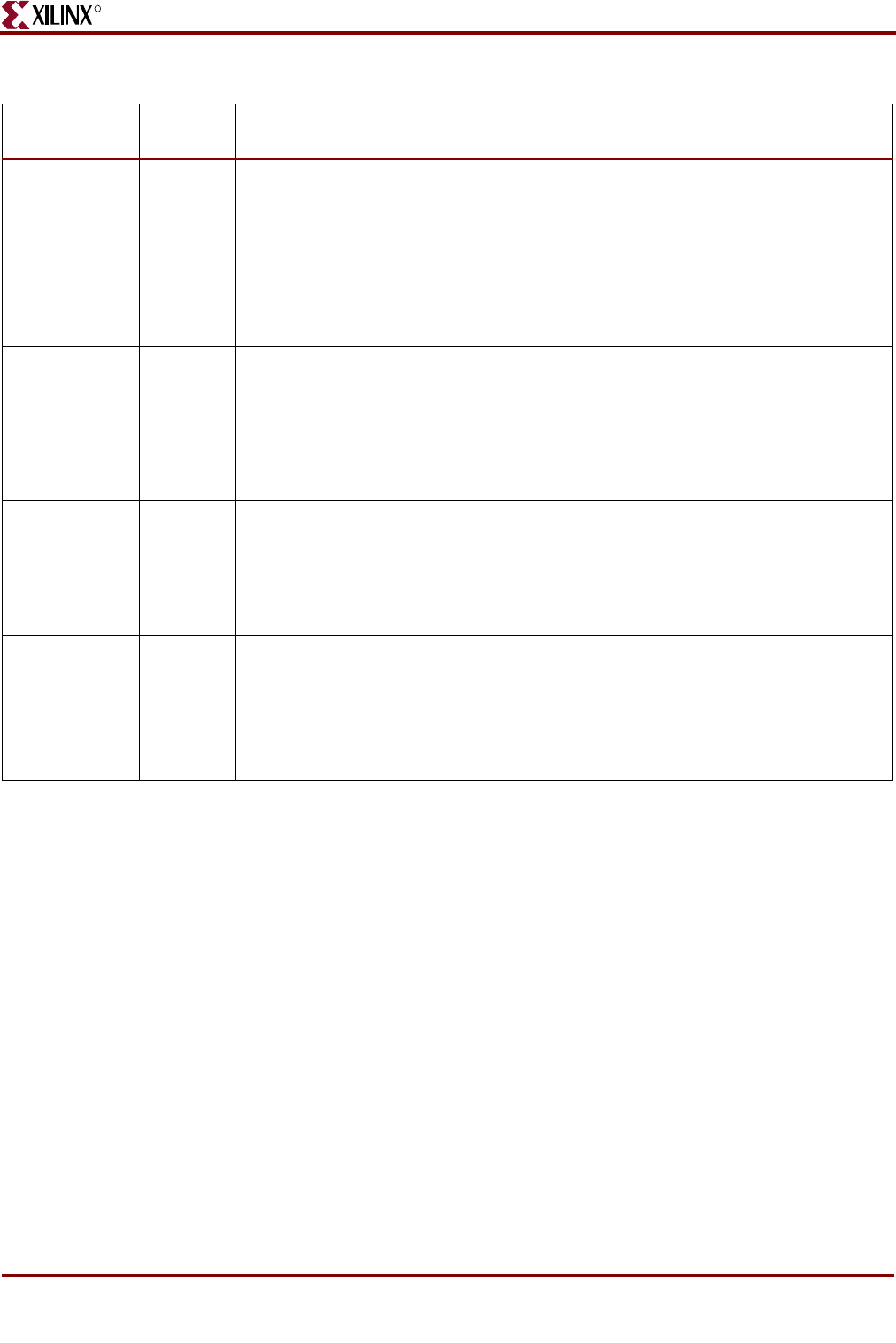

SrcPatternErr Output SrcFFClk Source Data Pattern Error: When this signal is asserted (active high), it

indicates that the data pattern written into the Source FIFO is illegal. Illegal

patterns include the following:

• Burst of data terminating on a non-credit boundary (not a multiple

of 16 bytes) with no EOP

• Non-zero value on SrcFFMod when SrcFFEOP is deasserted

This signal is asserted for one clock cycle each time an illegal data pattern is

written into the Source FIFO.

IdleRequest Input SrcFFClk Idle Request: This is an active high signal that requests idle control words be

sent out of the Source SPI-4.2 interface. The Source core responds by sending

out idle control words at the next burst boundary. This signal overrides normal

SPI-4.2 data transfer requests, but it does not override training sequence

requests (TrainingRequest).

Activating the request for idle cycles does not affect the Source FIFO contents

or the user side operation.

TrainingRequest Input SrcFFClk Training Pattern Request: This is an active high signal that requests training

patterns be sent out of the Source SPI-4.2 interface. The Source core responds

by sending out training patterns at the next burst boundary. This signal

overrides idle requests (IdleRequest) and normal SPI-4.2 data transfers.

Activating the request for training cycles does not affect the Source FIFO

contents or the user side operation.

SrcTriStateEn Input SrcFFClk SrcTriStateEn: This is an active high control signal that enables you to tri-state

the IOB drivers for the following Source core outputs: TDClk, TDat[15:0], and

TCtl.

When SrcTriStateEn=0 the outputs are not tri-stated.

When SrcTriStateEn=1 the outputs are tri-stated.

Default setting for this signal is disabled (SrcTriStateEn=0.)

Table 2-11: Source Control and Status Signals (Continued)

Name Direction

Clock

Domain

Description