SPI-4.2 Lite v4.3 User Guide www.xilinx.com 39

UG181 June 27, 2008

Source Core Interfaces

R

Source Clocking Interface

The Source core supports two clocking implementations: master clocking and slave

clocking. The master clocking configuration provides a complete solution with the clock

circuitry embedded within the Source core. The slave clocking configuration allows the

clocking scheme to be implemented external to the Source core.

A list of the Source clocks for master clocking and their description is provided in

Table 2-16. Table 2-17 defines the Source Core clock status signals, and Table 2-18 defines

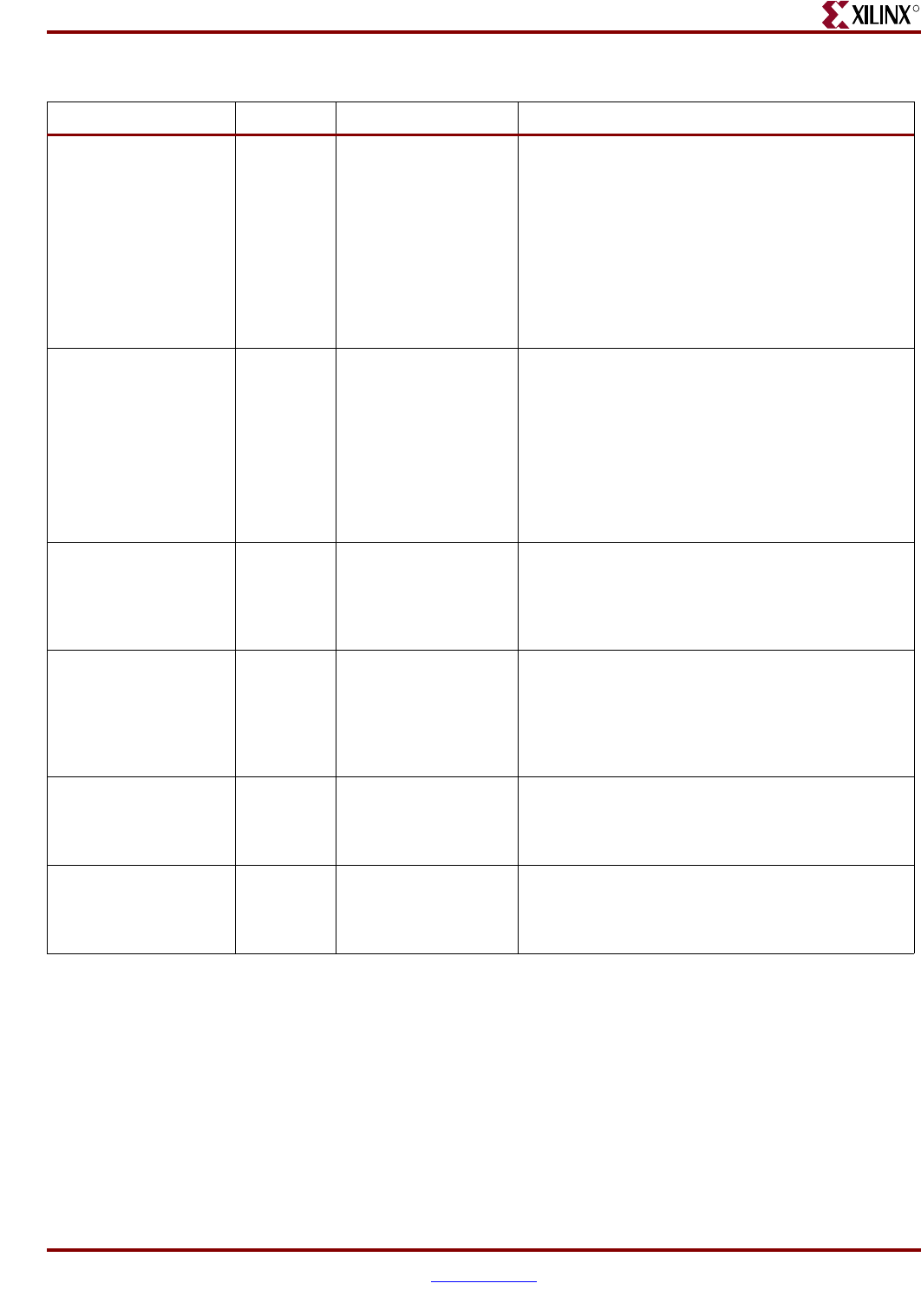

SrcCalendar_M[7:0] Input 0-255

(effective range 1-256)

Source Calendar Period: The SrcCalendar_M

parameter sets the number of repetitions of the calendar

sequence before the DIP-2 parity and framing words are

received.

The Source core implements this parameter as a static

register synchronous to SrcStatClk, and it can be

updated in circuit by first deasserting SrcEn.

Note that the Source Calendar Period equals

SrcCalendar_M + 1. For example, if SrcCalendar_M=22,

the Source Calendar Period will be equal to 23.

SrcCalendar_Len[8:0] Input 0-511

(effective range 1-512)

Source Calendar Length: The SrcCalendar_Len

parameter sets the length of the calendar sequence.

The Source core implements this parameter as a static

register synchronous to SrcStatClk, and it can be

updated in circuit by first deasserting SrcEn.

Note that the Source Calendar Length equals

SrcCalendar_Len + 1. For example, if

SrcCalendar_Len=15, the Source Calendar Length will

be equal to 16.

DataMaxT[15:0] Static Input 0, 16-65535 Maximum Data-Training Interval: Maximum interval

between scheduling of training sequences on the SPI-

4.2 data path (in SPI-4.2 bus cycles). Note that setting

DataMaxT to zero configures the core to never send

periodic training.

AlphaData[7:0] Static Input 0-255 Data Training Pattern Repetitions: Number of

repetitions of the 20-word data training pattern. Note

that setting AlphaData to zero configures the core to not

periodically send training patterns. In this case, you can

manually send training patterns by asserting the

TrainingRequest command.

NumDip2Errors[3:0] Static Input 1-15

Value equal to 0 gets set

to 1

Number of DIP-2 Errors: The Source Interface will go

out-of-frame (SrcOof asserted) and stop transmitting

SPI-4.2 data across the data bus after receiving

NumDip2Errors consecutive DIP-2 errors.

NumDip2Matches[3:0] Static Input 1-15

Value equal to 0 gets set

to 1

Number of DIP-2 Matches: The Source Interface

requires NumDip2Matches consecutive DIP-2 matches

before going in-frame and beginning to transfer SPI-4.2

data across the SPI-4.2 data bus.

Table 2-15: Source Static Configuration Signals (Continued)

Name Direction Range Description