86 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 4: Designing with the Core

R

To enable designing back-end user logic, the Source core presents status information in two

ways:

• Addressable Status Interface. This interface allows polling the status of 16 channels

at a time. This polling is synchronous to a user-defined clock (SrcStatClk).

Additionally, the last channel receiving a status update on TStat[1:0] is presented

(synchronous to TSClk).

• Transparent Status Interface. This interface presents status information as it is

received on TStat[1:0] with minimal latency. It also provides the ideal interface to

customize how to process the FIFO status information as it is received.

A user-programmable calendar is also provided. This calendar stores the order and

frequency that each channel status that is received on TStat, which is identical to the

sequence defined by the device that is receiving data from the Source interface. This is the

mechanism that enables the interfaces to determine which channel status is being received

on TStat. As defined by the SPI-4.2 specification, there are two bits provided for each

channel, indicating the channel status (hungry=01, starving=00, satisfied=10).

These interfaces are described in greater detail in the following sections. Descriptions of

the Source Status Path signals are provided in Table 2-13 and Table 2-14, page 36.

Source Calendar Initialization

There are two ways to initialize the Source calendar. The calendar can be initialized by

loading the COE file in the CORE Generator GUI. This loads the calendar contents into the

UCF file. For more information, see Chapter 3, “Generating the Core.” If this method is not

used, the calendar must be initialized in-circuit at startup.

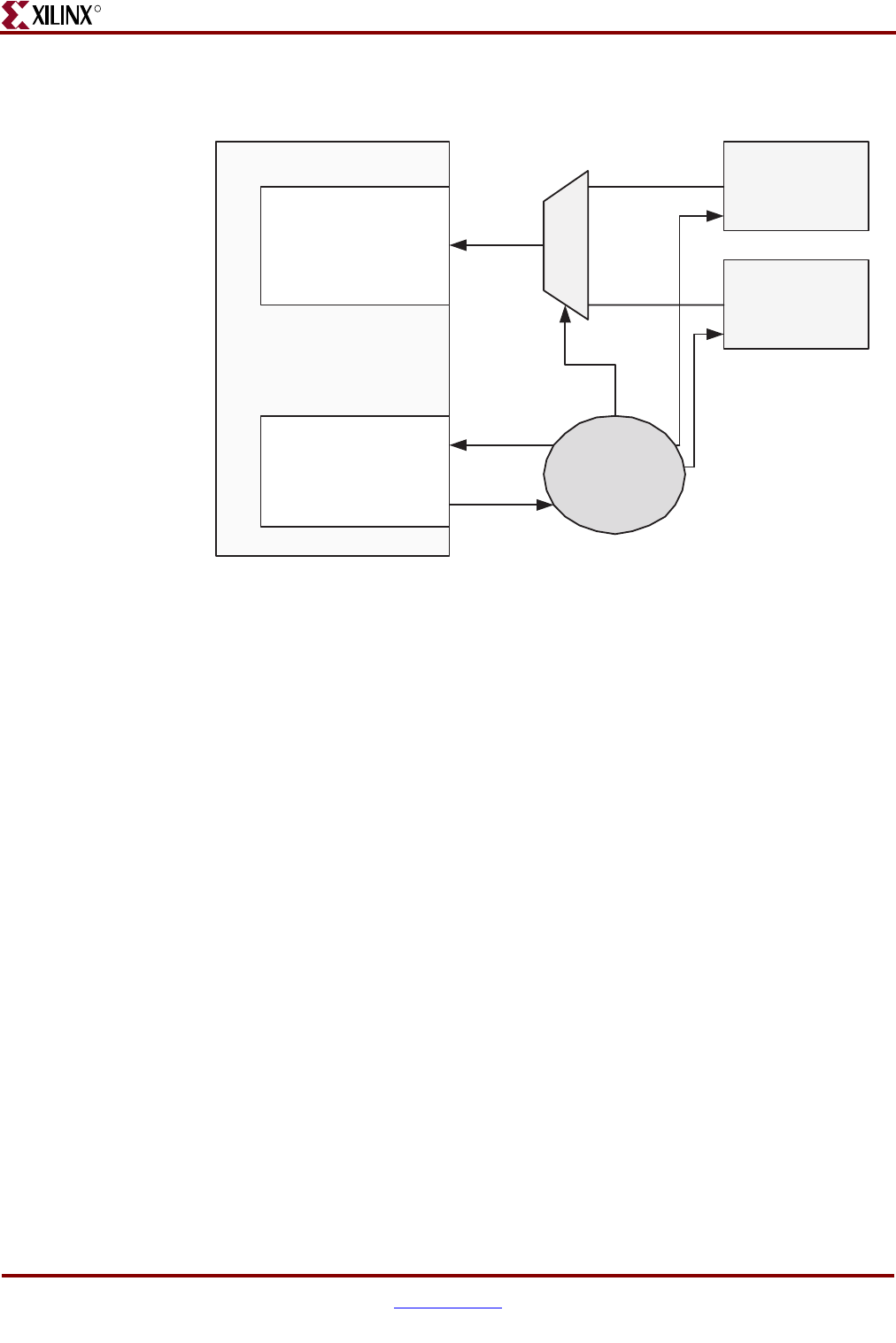

Figure 4-27: Typical User Design Example

POLLING

Source Core

FIFO

Status I/F

FIFO

Channel 0

FIFO

Channel 1

User

Interface

MUX

Arbiter