30 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 2: Core Architecture

R

Source Core Interfaces

The Source core includes five functional modules:

• Source Data FIFO

• Source Data Transmit

• Source Status Registers

• Source Calendar

• Source Status Receive

The Source core is comprised of the following interfaces:

• Source SPI-4.2 Interface

• Source User Interface

♦ Source Control and Status Interface

♦ Source FIFO Interface

♦ Source Status and Flow Control Interface

- Calendar Control Interface

- Status FIFO Interface

♦ Source Configuration Signals Interface

♦ Source Clocking Interface

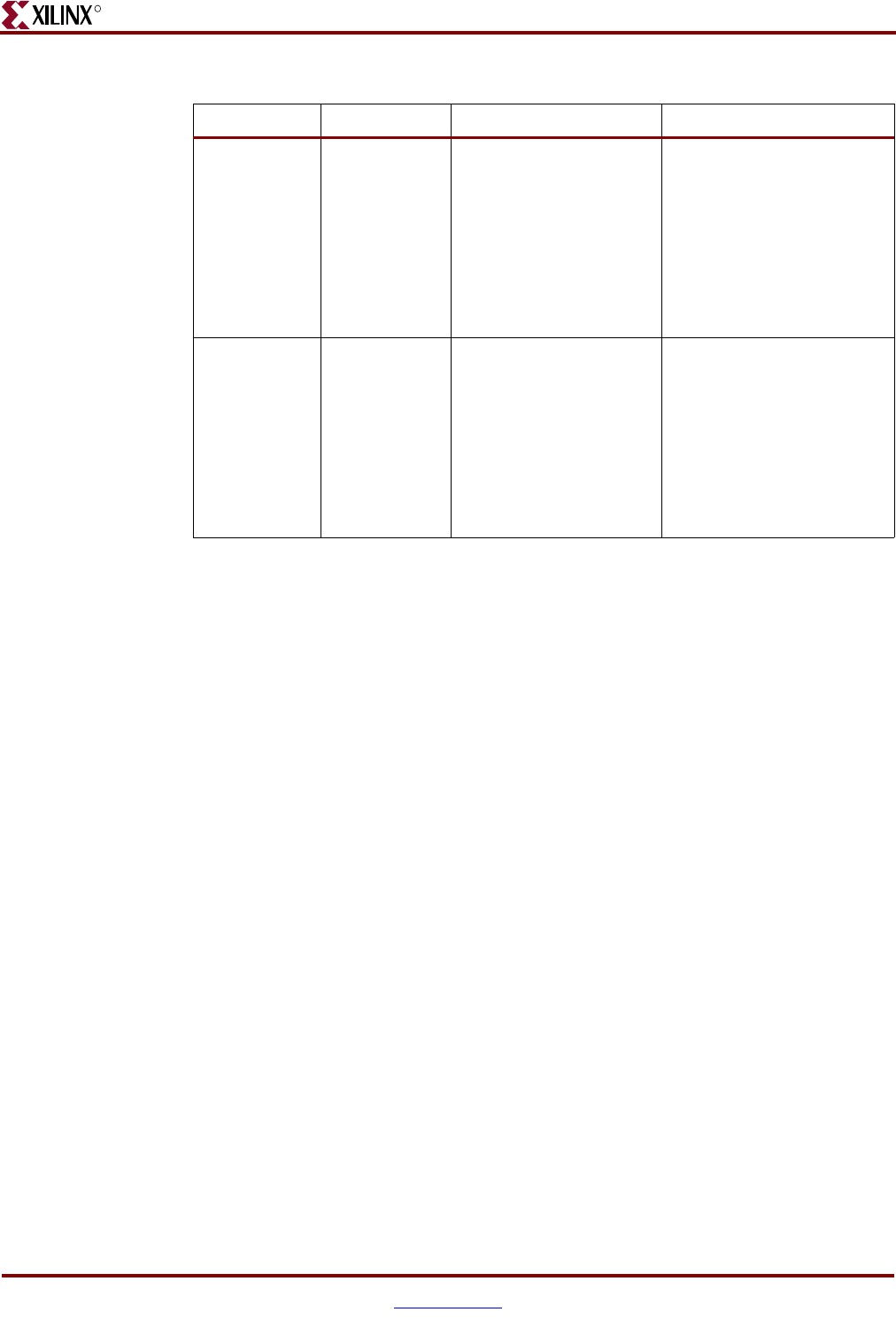

Table 2-9: Sink Core Clocks: User Clocking

Clock Pins Direction Description Max. Frequency

RDClk0_USER Input

(User Interface)

RDClk0_USER: This clock

is used for clocking the

internal logic of the core.

Virtex-5: 275 MHz

Virtex-4: 190 MHz

Virtex-II Pro: 160 MHz

Virtex-II: 160 MHz

Spartan-3: 115 MHz

Spartan-3E: 90 MHz

Spartan-3A/3AN/3A DSP:

105 MHz

RDClk180_USE

R

Input

(User Interface)

RDClk180_USER: This

clock is the inverted

equivalent of

RDClk0_USER. It is used

for clocking the internal

logic of the core.

Virtex-5: 275 MHz

Virtex-4: 190 MHz

Virtex-II Pro: 160 MHz

Virtex-II: 160 MHz

Spartan-3: 115 MHz

Spartan-3E: 90 MHz

Spartan-3A/3AN/3A DSP:

105 MHz