68 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 4: Designing with the Core

R

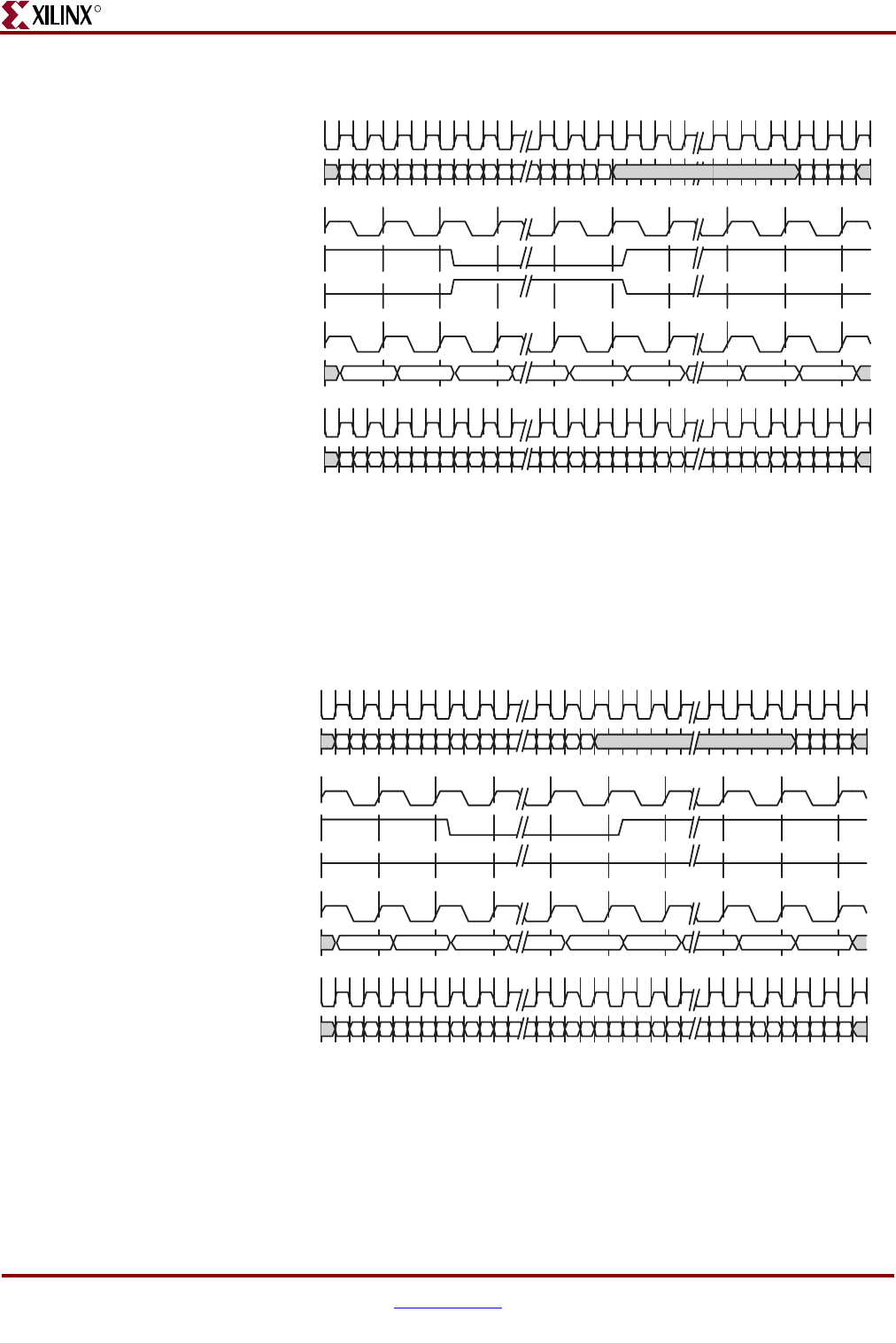

FIFO Almost Full Mode “01”

When the FIFO Almost Full Mode (FifoAFMode) is set to “01,” and the Sink core becomes

Almost Full, the Sink interface remains in-frame (SnkOof deasserted), and the Sink Status

logic sends satisfied (“10”) on all channels until SnkAlmostFull_n is deasserted. This is

illustrated in Figure 4-13.

Figure 4-12: FIFO Almost Full Mode “00”

Figure 4-13: FIFO Almost Full Mode “01”

D D

11 11

D D D D D D D DD D DRDat_P

RDClk_P

D

SnkAlmostFull_n

SnkFFClk

00 00 00 00RStat

RSClk

SnkStat

SnkStatClk

00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 11 11 11 11 11 11 11 11 11 11 11

SnkOof

D D D D

00 00 000000 00 00

D D D D D

D D

10 10

D D D D D D D DD D DRDat_P

RDClk_P

D

SnkAlmostFull_n

SnkFFClk

00 00 00 00RStat

RSClk

SnkStat

SnkStatClk

00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 10 10 10 10 10 10 10 10 10 10 10 10

SnkOof

D D D D

00 00 000000 00 00

D D D D