60 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 4: Designing with the Core

R

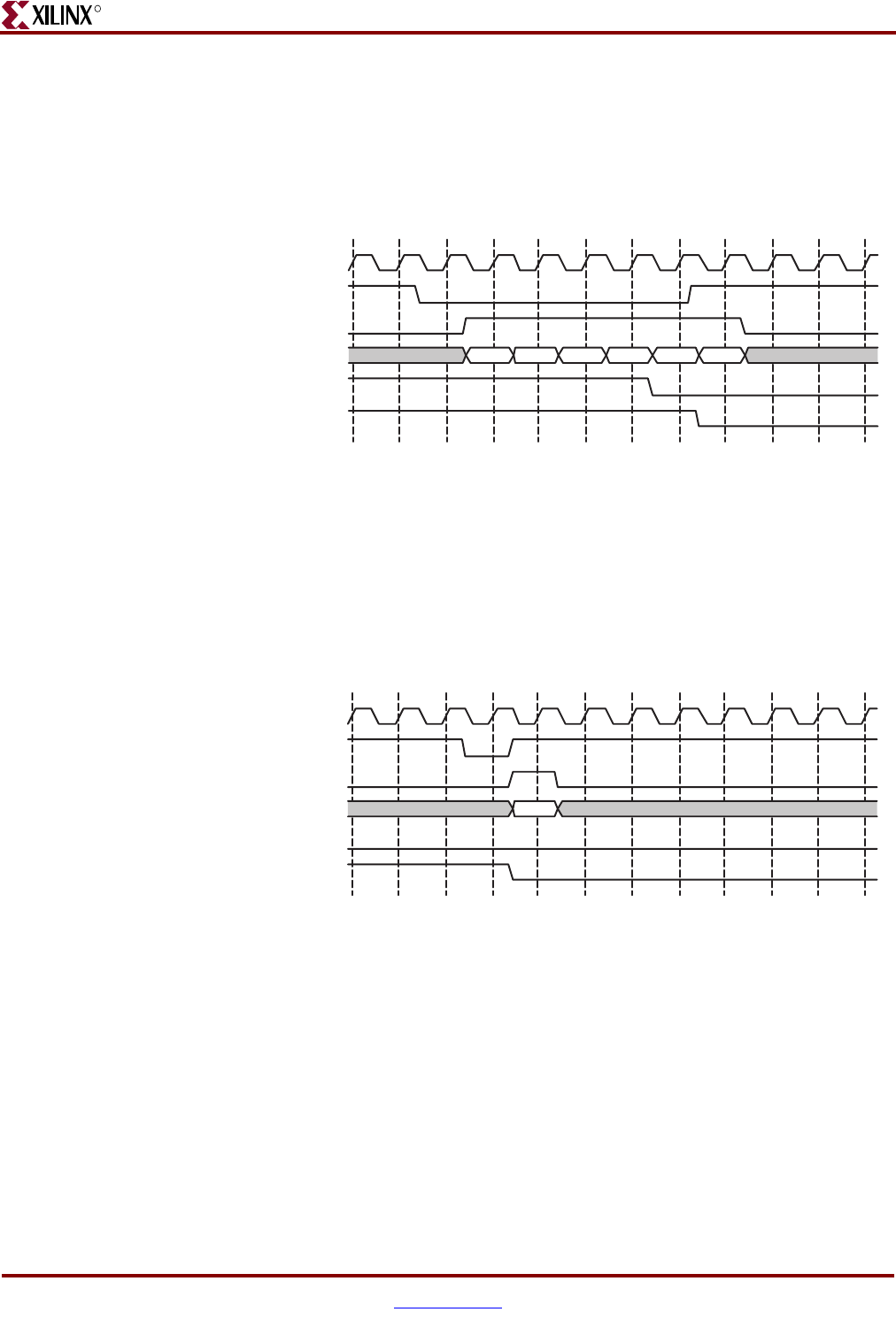

deasserted on the next clock cycle. The Sink FIFO read logic should then evaluate the

SnkFFEmpty_n signal to verify that there is no data in the FIFO in case an additional word

was simultaneously written into the FIFO. An example of this is provided with the SPI-4.2

Lite core in the Design Example (see the pl4_lite_fifo_loopback_read.v/vhd file.)

This example also illustrates the Sink FIFO Valid signal, which is asserted while there is

valid data on the data bus.

Sink FIFO Empty

Figure 4-5. illustrates the behavior of the Empty (SnkFFEmpty_n) status signal. As shown

in the waveform, the empty flag is asserted with the last word read out of the FIFO. In this

example, the Almost Empty flag is asserted prior to a read access being initiated. In this

case, there is one data word remaining in the FIFO. To access this word, assert the Sink

FIFO Read Enable (SnkFFRdEn_n) signal for one cycle.

Sink Almost Full

The behavior of Sink Almost Full flag (SnkAlmostFull_n) is dependent on the static

configuration signals SnkAFThresAssert and SnkAFThresNegate. When the

SnkAlmostFull_n flag is asserted, SnkAFThresAssert specifies the number of empty

FIFO locations available. For a 64-bit user interface, each FIFO location can contain up to

1/2 of a credit (8 bytes) worth of data from a single packet. For a 32-bit user interface, each

FIFO location can contain up to 1/4 of a credit (4 bytes) worth of data from a single packet.

SnkAFThresNegate specifies when the SnkAlmostFull_n flag is deasserted.

The number of bytes that can be written into the Sink SPI-4.2 interface after the Sink

Almost Full flag is asserted depends on received packet sizes, data patterns, and

Figure 4-4: Sink FIFO Almost Empty

Figure 4-5: Sink FIFO Empty

SnkFFData

SnkFFRdEn_n

SnkFFClk

SnkFFAlmostEmpty_n

SnkFFValid

SnkFFEmpty_n

SnkFFData

SnkFFRdEn_n

SnkFFClk

SnkFFAlmostEmpty_n

SnkFFValid

SnkFFEmpty_n