SPI-4.2 Lite v4.3 User Guide www.xilinx.com 113

UG181 June 27, 2008

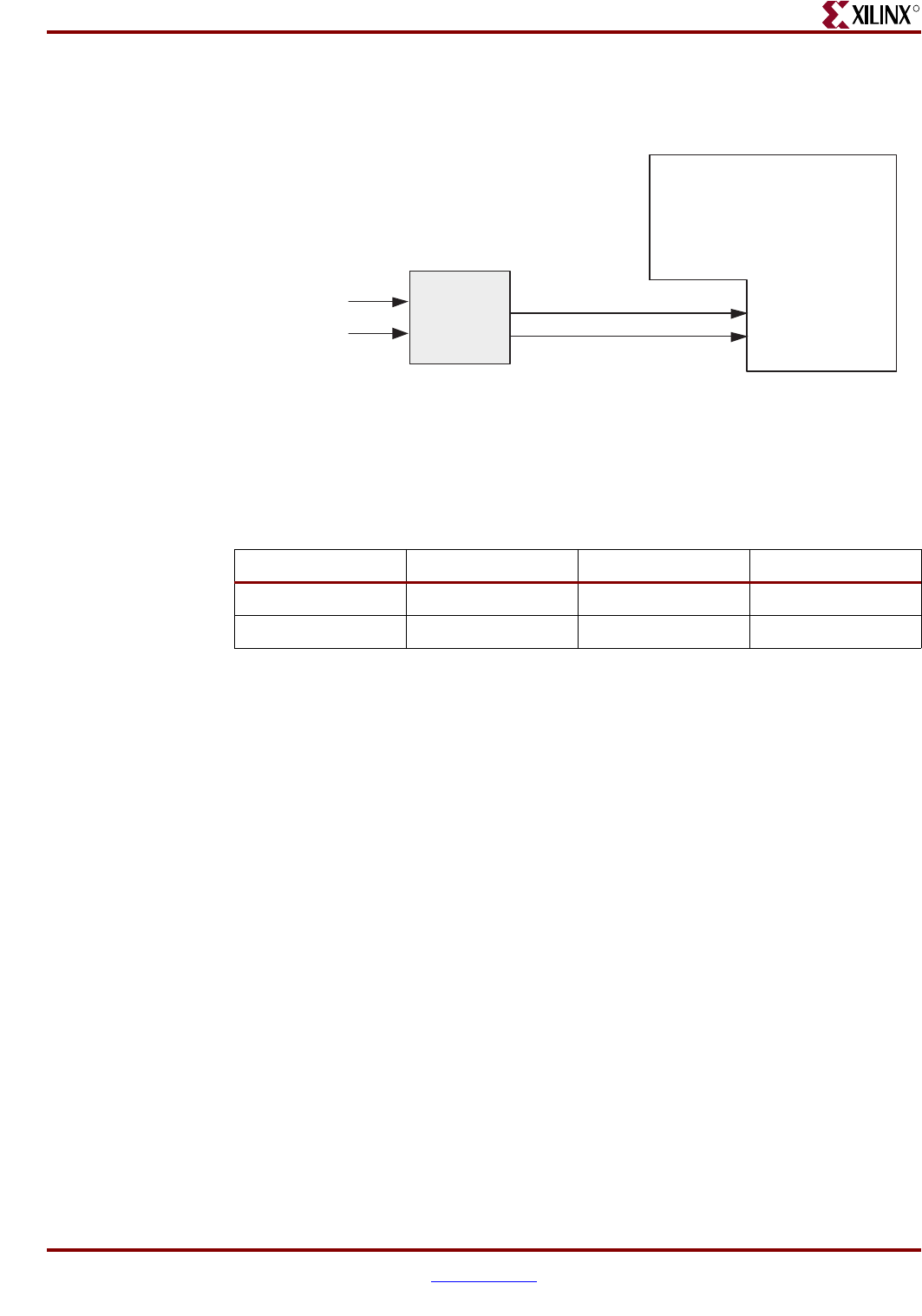

Sink Clocking Options

R

defined in Table 2-9, page 30. For all architectures other than Virtex-4 or Virtex-5 devices,

user clocking can only be implemented using global clocking resources.

When targeting the Virtex-4 and Virtex-5 device architectures, the user clocking module

can be configured to use global or regional clocking distribution. Table 6-2 provides the

clocking resource count for the user clocking configurations.

Global Clocking

This implementation uses the DCM and global clock routing to generate a full-rate clock

(RClk0_USER) and inverted full-rate clock (RDClk180_USER). This configuration is

illustrated in Figure 6-3. Note that the inverter used to generate the RDClk180_USER clock

will be absorbed into the DDR flops.

Figure 6-2: Example: Sink User Clocking Inputs

Table 6-2: Sink Core User Clocking Resources

Clocking Option BUFR BUFG DCM

Global clocking 0 1 1

Regional clocking 1 1

a

a. The Sink core requires the SnkIdelayRefClk clock (200 MHZ reference clock to be driven by a global

clock buffer. This reference clock provides a time reference to IDELAYCTRL modules to calibrate all the

individual delay elements (IDELAY) in the region. Multiple cores need only one global clock buffer to

distribute the SnkIdelayRefClk clock.

0

User

Clocking

Example

Module

RDClk_P

RDClk_N

RDClk0_user

RDClk180_user

RDClk0_USER

RDClk180_USER

SPI-4.2 Lite Sink Core

(Configured with User Clocking)