66 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 4: Designing with the Core

R

Sink Status FIFO Status Interface: Example 3

This example illustrates status received on the user interface and written to the SPI-4.2 bus.

Figure 4-11 shows a RStat waveform for a calendar length of four

(SnkCalendar_Len=3) and calendar repetition value of one (SnkCalendar_M=0). Note

that FIFO status information is periodic, repeating the sequence of a framing pattern (11),

a repeated set of FIFO status words (SnkCalendar_M + 1 times) in accordance with the

programmed calendar order, and a DIP-2 value. The programmed calendar sequence is

channel 0, 1, 2, 3, and the following RStat[1:0] sequence is illustrated:

• Sequence #: CH0, CH1, CH2, CH3

• Sequence 1: 10, 00, 00, 00

• Sequence 2: 10, 00, 10, 10

• Sequence 3: 10, 10, 10, 10

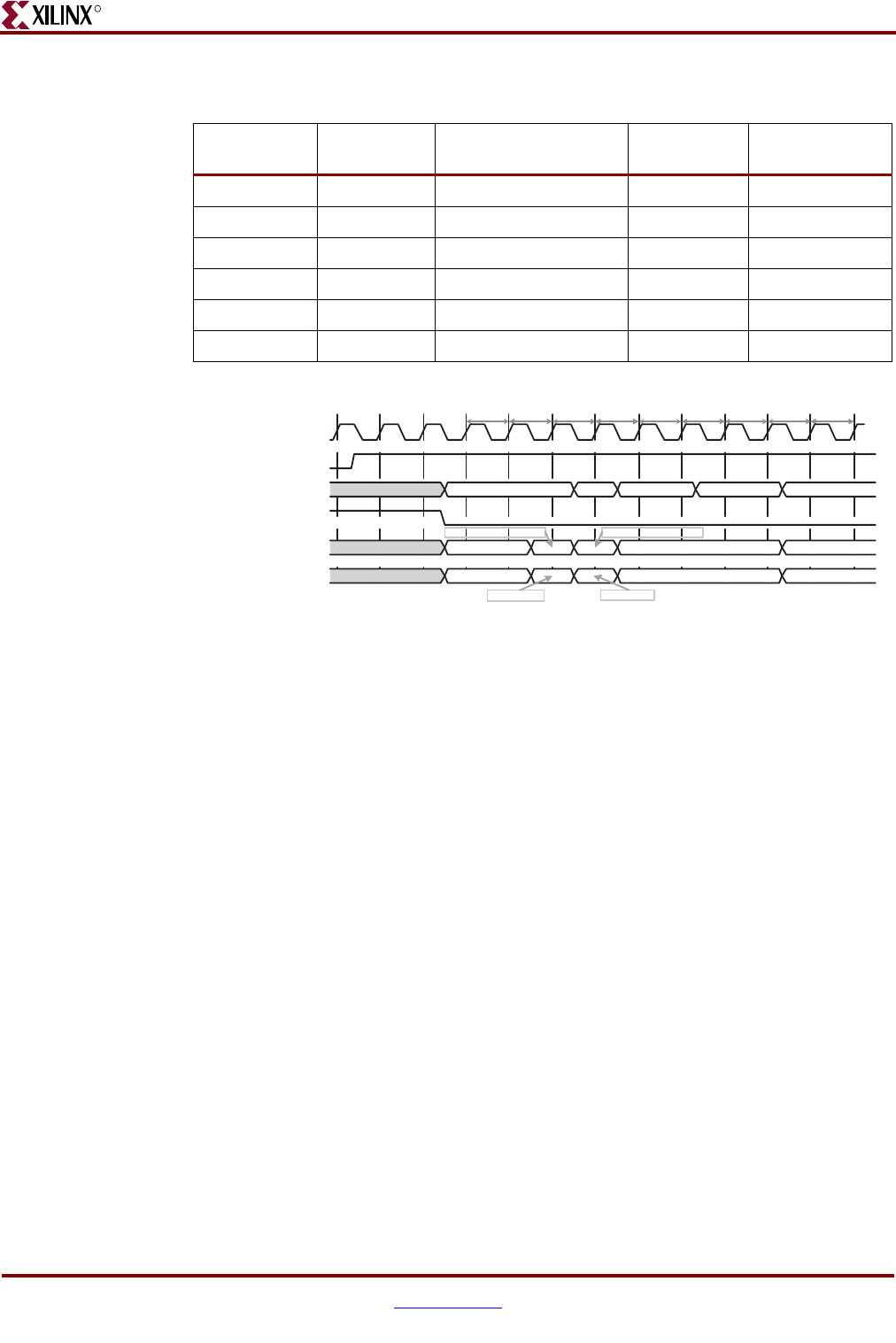

Table 4-5: Status Written to Status FIFO Interface

Write Cycle

Status

Address

Status Mask

Starving

Status

Satisfied Status

0-1 Bank 0 1111.1111.1111.1111 CH 0-15 none

2 Bank 0 0000.0000.0000.0001 none CH 0

3 Bank 1 1000.0000.0000.0000 none CH 31

4-5 Bank 2 1111.1111.1111.1111 CH 32-47 none

6-7 Bank 3 1111.1111.1111.1111 CH 48-63 none

8-9 Bank 0 1111.0000.0000.0000 none CH 12-15

Figure 4-10: Sink Status FIFO Interface Example: 64-channel Configuration

SnkStatClk

SnkStatMask[15:0]

SnkStatAddr[3:0]

SnkStat[31:0]

SnkEn

SnkStatWr_n

Write 0 Write 1 Write 2 Write 3 Write 4 Write 5 Write 6 Write 7 Write 8

BINARY

0000BINARY 0001 0010 0011

HEX 0000.0000

0000

0000.0000

1111.0000.0000.0000

0000.0000.0000.0001

8000.00000000.0002

1111.1111.1111.1111

1111.1111.1111.1111

AA00.0000

1000.0000.0000.0000