SPI-4.2 Lite v4.3 User Guide www.xilinx.com 19

UG181 June 27, 2008

Sink Core Interfaces

R

standard FIFO interface, and the FIFO read and write operations are performed in

independent clock domains.

The Source core implements the following features:

• Supports 32-bit or 64-bit user data width.

• Optionally transmits only complete data bursts.

• Provides both master and slave clocking to facilitate multiple core implementations.

• Enables addressable or transparent access to SPI-4.2 flow control data.

• Provides a FIFO reset signal for clearing contents of the data pipe during operation.

• Provides support for forcing the insertion of DIP-4 errors for system testing.

For more information on core features, see Chapter 4, “Designing with the Core.”

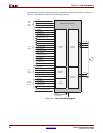

Sink Core Interfaces

The Sink core has five functional modules:

• Sink Data FIFO

• Sink Data Receive

• Sink Status Registers

• Sink Calendar

• Sink Status Transmit

The Sink core has the following interfaces:

• Sink SPI-4.2 Interface

• Sink User Interface

♦ Sink Control and Status Interface

♦ Sink FIFO Interface

♦ Sink Status and Flow Control Interface

- Calendar Control Interface

- Status FIFO Interface

♦ Sink Configuration Interface

♦ Sink Clocking Interface