SPI-4.2 Lite v4.3 User Guide www.xilinx.com 37

UG181 June 27, 2008

Source Core Interfaces

R

Source Static Configuration Interface

These signals are inputs to the core that are statically driven by setting them to a constant

value in the top-level wrapper file. The SPI-4.2 Lite release includes a wrapper file that has

the static configuration signals connected to the values selected in the CORE Generator

GUI. Customization of these signals is done using the GUI.

Three of the Source Static Configuration signals can be changed in-circuit. There are static

registers for

SrcBurstLen (synchronous to SrcFFClk), and SrcCalendar_M and

SrcCalendar_Len (synchronous to SrcStatClk.) To change these parameters while the

core is operational, you must first deassert

SrcEn.

SrcStatAddr[3:0]

(Addressable I/F

Only)

Input SrcStatClk Source Status Address:

For the Addressable Interface, the Source Status Address determines

which group of 16-channels gets its status driven onto SrcStat on the

following clock cycle. The address bus is associated with banks of

channels as follows:

Bank 0: SrcStatAddr=0 channel 15-0

Bank 1: SrcStatAddr=1, channel 31-16

Bank 2: SrcStatAddr=2, channel 47-32

...

Bank 15: SrcStatAddr=15 channel 255-240

For the Transparent Interface, this signal is not present.

SrcStatCh[7:0] Output TSClk_GP Source Status Channel: The Source Status Channel is an 8-bit bus

containing the channel address that is being updated on the

SrcStatAddr bus in the current clock cycle.

SrcStatChValid Output TSClk_GP Source Status Channel Valid: When asserted, Source Status Channel

Valid indicates that the value on SrcStatCh is valid. When the core is

processing DIP-2 or frame words, SrcStatChValid is deasserted. Note

that a transition of the SrcStatChValid from 0 to 1 indicates that the

core has started a new calendar sequence.

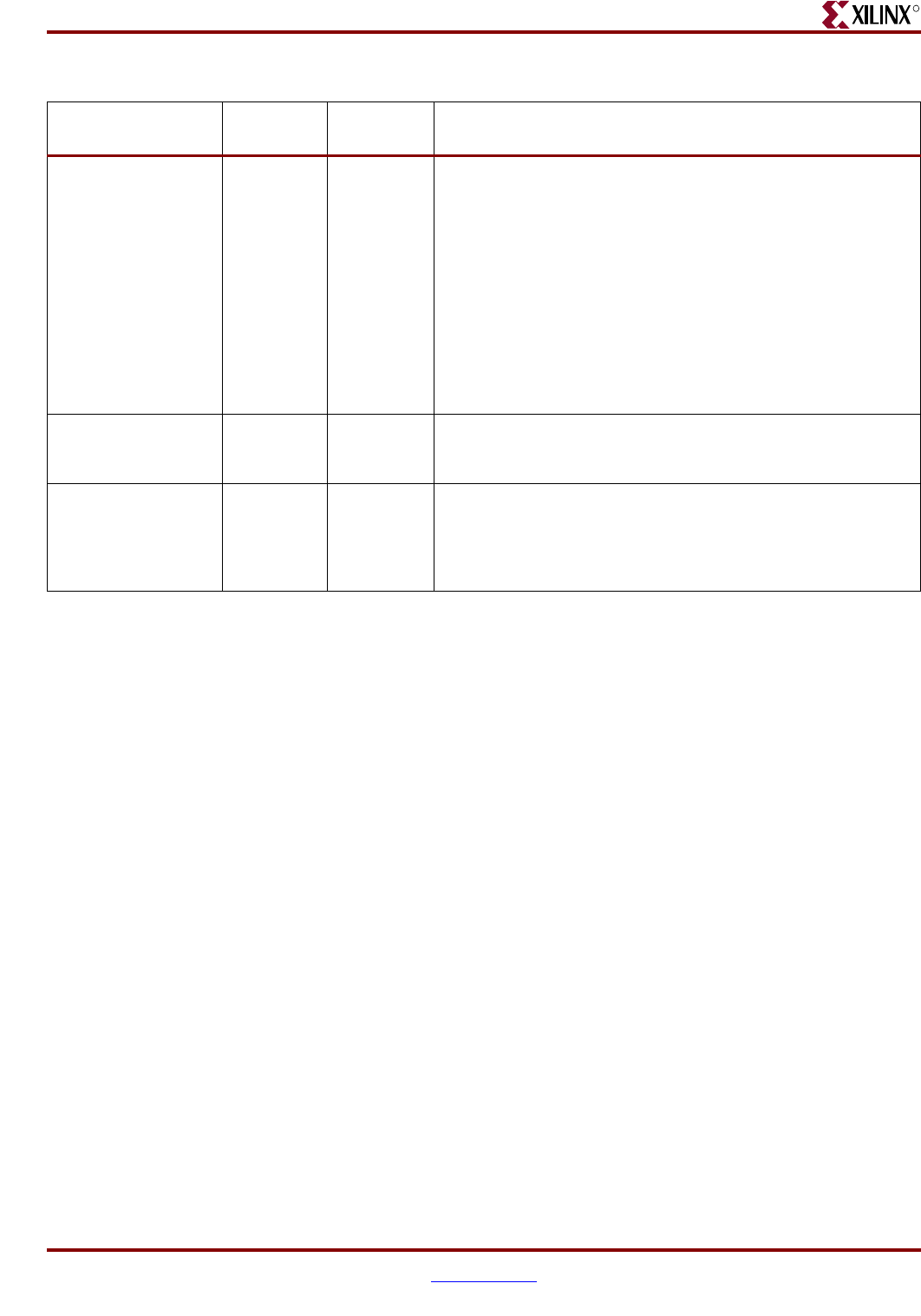

Table 2-14: Source Status FIFO Signals (Continued)

Name Direction

Clock

Domain

Description