20 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 2: Core Architecture

R

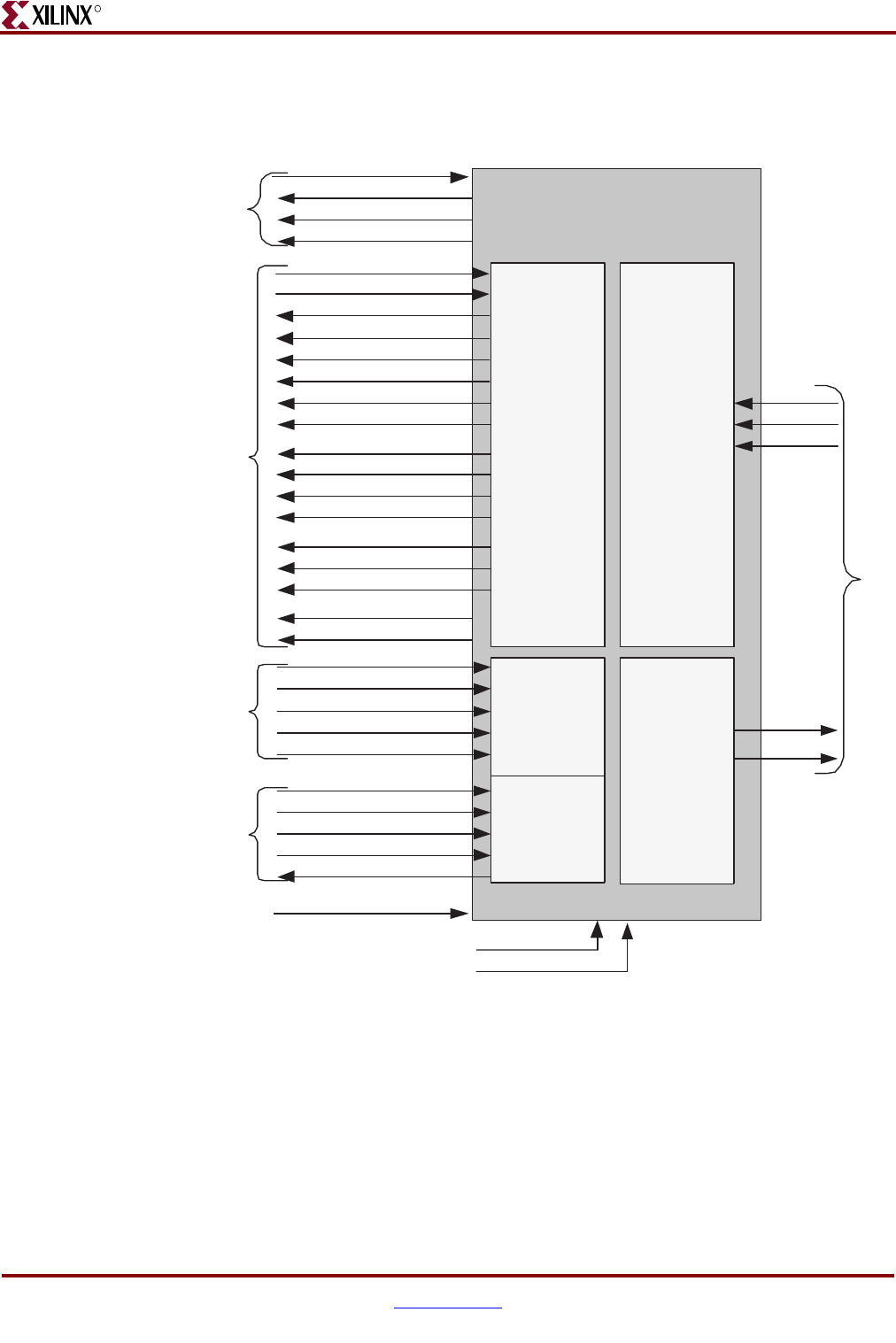

The functional modules and signals which comprise the different interfaces are shown in

Figure 2-2 and defined in tables in the following sections.

Figure 2-2: Sink Core Block Diagram

SPI-4.2 Lite Sink Core

Sink Data

Receive

Sink Data

FIFO

Sink Status

Transmit

Sink Status

Registers

Sink

Calendar

SPI-

4

Sin

Interf

a

FIFO

nterface

FIFO

Status

nterface

Control

and

Status

nterface

C

alendar

Control

nterface

Reset_n

SnkFifoReset_n

RDClk

RDat[15:0]

RSClk

RStat[1:0]

RCtl

SnkFFClk

SnkFFRdEn_n

SnkFFAddr[7:0]

SnkFFData[63:0] or [31:0]

SnkFFMod[2:0] or [1:0]

SnkFFSOP

SnkFFEmpty_n

SnkFFErr

SnkFFEOP

SnkFFAlmostEmpty_n

SnkStatClk

SnkStatAddr[3:0]

SnkCalClk

SnkCalWrEn_n

SnkCalAddr[8:0]

SnkCalData[7:0]

SnkTrainValid

SnkFFDIP4Err

SnkEn

SnkAlmostFull_n

SnkBusErr

Static Configuration Signals

SnkFFValid

SnkOverflow_n

SnkOof

SnkFFPayloadErr

SnkCalDataOut[7:0]

SnkStat[31:0]

SnkStatWrEn_n

SnkStatMask[15:0]

SnkFFPa

yloadDIP4

SnkFFBurstErr