SPI-4.2 Lite v4.3 User Guide www.xilinx.com 93

UG181 June 27, 2008

Source Core

R

Source Static Configuration Signals

The source static configuration signals are inputs to the core, statically driven to determine

the behavior of the core. See Table 2-15, page 38 for a full list of static configuration signals.

Three of the Source Static Configuration signals can be changed in-circuit. There are static

registers for SrcBurstLen (synchronous to SrcFFClk), and SrcCalendar_M and

SrcCalendar_Len (synchronous to SrcStatClk.) To change these parameters while the

core is operational, first deassert SrcEn.

Source Burst Mode

Source Burst Mode (SrcBurstMode) is a static configuration signal that allows one to

define how data is transmitted by the Source core. If this signal is set to zero, the Source

core transmits data in the FIFO whenever there is a complete credit of data, or when there

is an end-of-packet flag (SrcFFEOP.) This is compliant with the transmit operation as

defined by the SPI-4.2 OIF specification. If a partial credit is written into the FIFO and then

paused, the data in the FIFO will be transmitted up to the last credit boundary.

When SrcBurstMode is set to 1, the Source core only transmits data that is terminated by

an EOP or when there is data in the FIFO equal to the maximum burst length defined by

the static configuration signal SrcBurstLen. If an incomplete burst is written into the

FIFO and paused, then data in the FIFO will be transmitted up to the last burst boundary.

When SrcBurstMode is set to 1, the Source FIFO thresholds (SrcAFThresAssert and

SrcAFThresNegate) must be greater than or equal to the burst length (SrcBurstLen).

If the FIFO thresholds are set to less than the burst length, the core will force the threshold

values to the burst length. This ensures that the FIFO will not report Almost Full before a

burst of data has been written into the core.

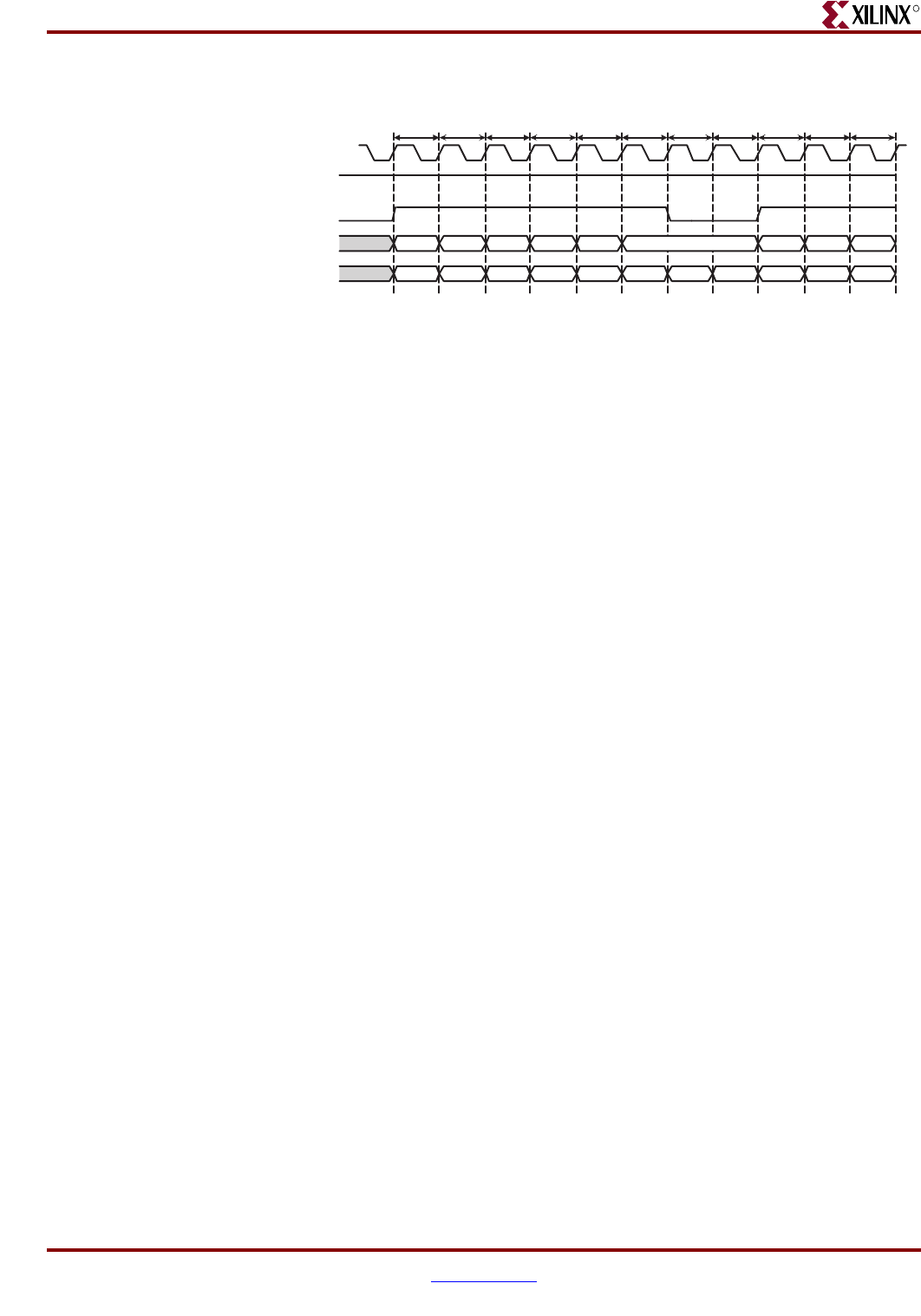

Figure 4-34: Transparent Source Status FIFO Interface: 256-channel Configuration

Read 0 Read 1 Read 2 Read 3 Read 4 Read 5 Read 6 Read 7 Read 8 Read 9 Rd 10

TSClk_GP

SrcStatCh[7:0]

DEC

SrcStat[1:0] BIN

SrcEn

SrcStatValid

0 2 128 129 10 79 169 1

01 10 00 01 01 10 01 11 00 01 10