SPI-4.2 Lite v4.3 User Guide www.xilinx.com 89

UG181 June 27, 2008

Source Core

R

The Source Status Channel (SrcStatCh[7:0]) indicates which channel status was last

updated on the SPI-4.2 Interface and is qualified by the Source Status Channel Valid signal

(SrcStatChValid=1). SrcStatChValid enables SrcStatCh[7:0] to be encoded,

and the valid signal is disabled when the core processes a received DIP-2 or framing word.

Note that the SrcStatusCh[7:0] and SrcStatChValid use the SPI-4.2 Interface clock

domain (TSClk_GP).

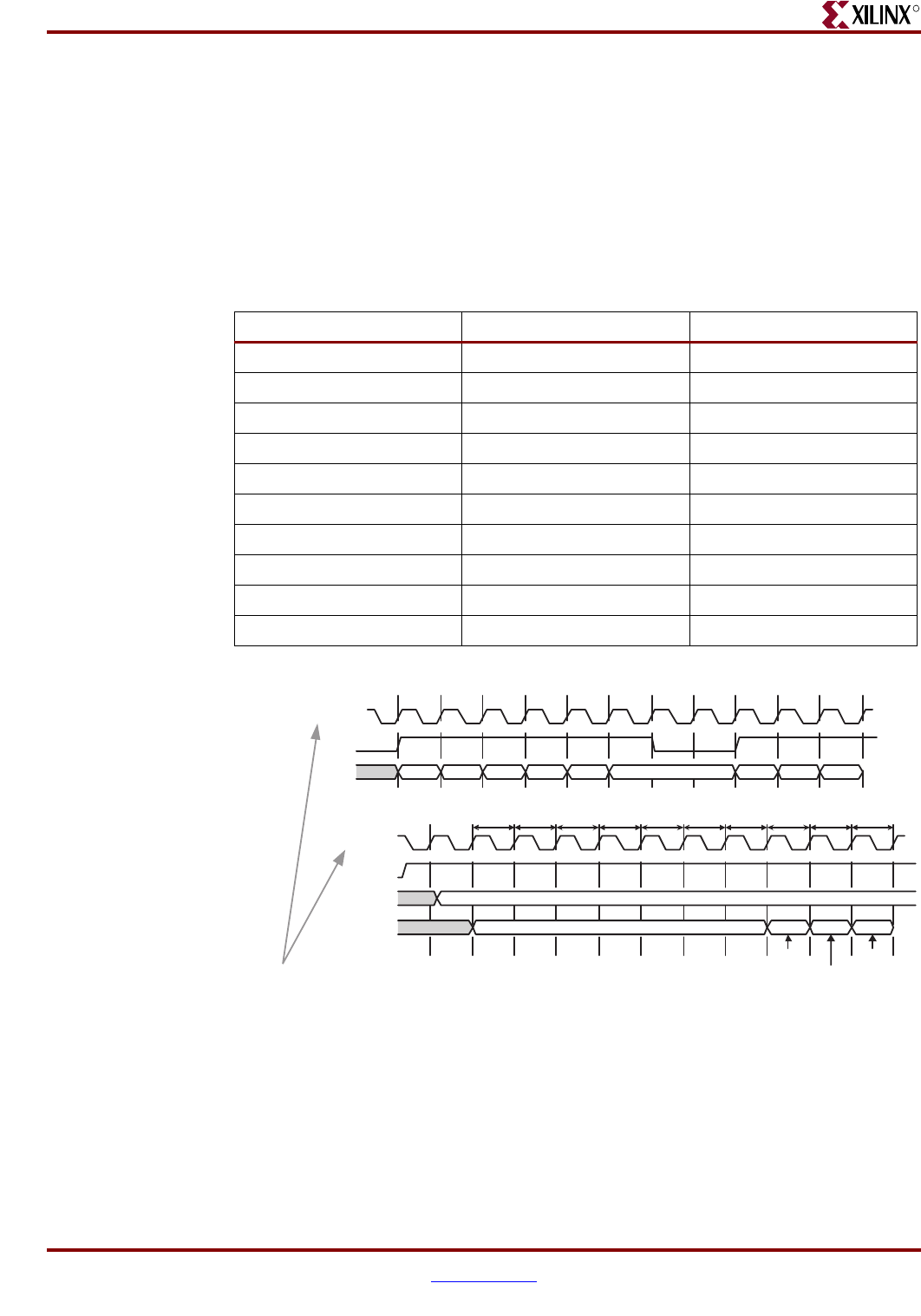

In this illustration, status is read for the 4-channel system. The calendar length is set to six

and programmed to round-robin this sequence: Ch0, Ch1, Ch2, Ch3, Ch0, Ch1.

Table 4-9

shows the status written into the SrcStat for each channel on every write clock cycle.

Addressable Status FIFO Interface: Example 2

This example illustrates reading the Status FIFO Interface for a 256-channel Source core,

shown in Figure 4-31. To read the status for 256 channels, address the following sixteen

banks—depending on the channel status is being read.

• Bank 0: SrcStatAddr[3:0]= 0000, for channels 15 to 0

Table 4-9: Status Written into SrcStat per Channel per Clock Cycle

Read Cycle Starving Status Satisfied Status

0CH 0-3none

1CH 0-3none

2CH 0-3none

3CH 0-3none

4CH 0-3none

5CH 0-3none

6CH 0-3none

7 CH 1-3 CH 0

8 CH 2-3 CH 0-1

9 CH 3 CH 0-2

Figure 4-30: Addressable Status FIFO Interface: 4-Channel Configuration

0x00000002

0x0000000A

0x0000002A

Read 0 Read 1 Read 2 Read 3 Read 4 Read 5 Read 6 Read 7 Read 8 Read 9

Independent

Clock

Domains

SrcStatAddr[3:0

]

BIN

SrcStat[31:0] HEX

SrcEn

0x00000000

0000

SrcStatClk

SrcStatCh[7:0] DEC

SrcStatValid

0 1 2 3 0 1 20 1

TSClk_GP