SPI-4.2 Lite v4.3 User Guide www.xilinx.com 95

UG181 June 27, 2008

Source Core

R

RESET

The Source core remains in the RESET state until the Reset_n signal is deasserted. When

in the RESET state, the Source core transmits idle patterns on TDat[15:0] and the Status

FIFO is driven to be satisfied (“10”) for all channels.

HUNT

When Reset_n is deasserted, the state machine goes to the HUNT state and sends

continuous training patterns on the SPI-4.2 Interface. Once the Source core is enabled

(SrcEn=1), the Source Status Interface attempts to acquire synchronization on the FIFO

Status Channel. When the Source Status Interface has found the “11” framing pattern, the

Source core and monitors for the programmed number of consecutive DIP-2 correct

matches (NumDip2Matches). When in the HUNT state, the Status FIFO is driven to be

satisfied (“10”) for all channels.

SYNC

If the number of correct DIP-2 matches are received (NumDip2Matches), the Source core

goes into the SYNC state. In this state, the core transmits the flow control data received on

the status path (TStat[1:0]) onto the user interface. It also transmits the data that has

been written into the FIFO on the SPI-4.2 Lite data bus (TDat[15:0]). If an incorrect

framing pattern (of four consecutive "11") is received, a set number of consecutive DIP-2

errors (defined by NumDip2Errors) are received, or if SrcEn is deasserted, the state

machine returns to the HUNT State.

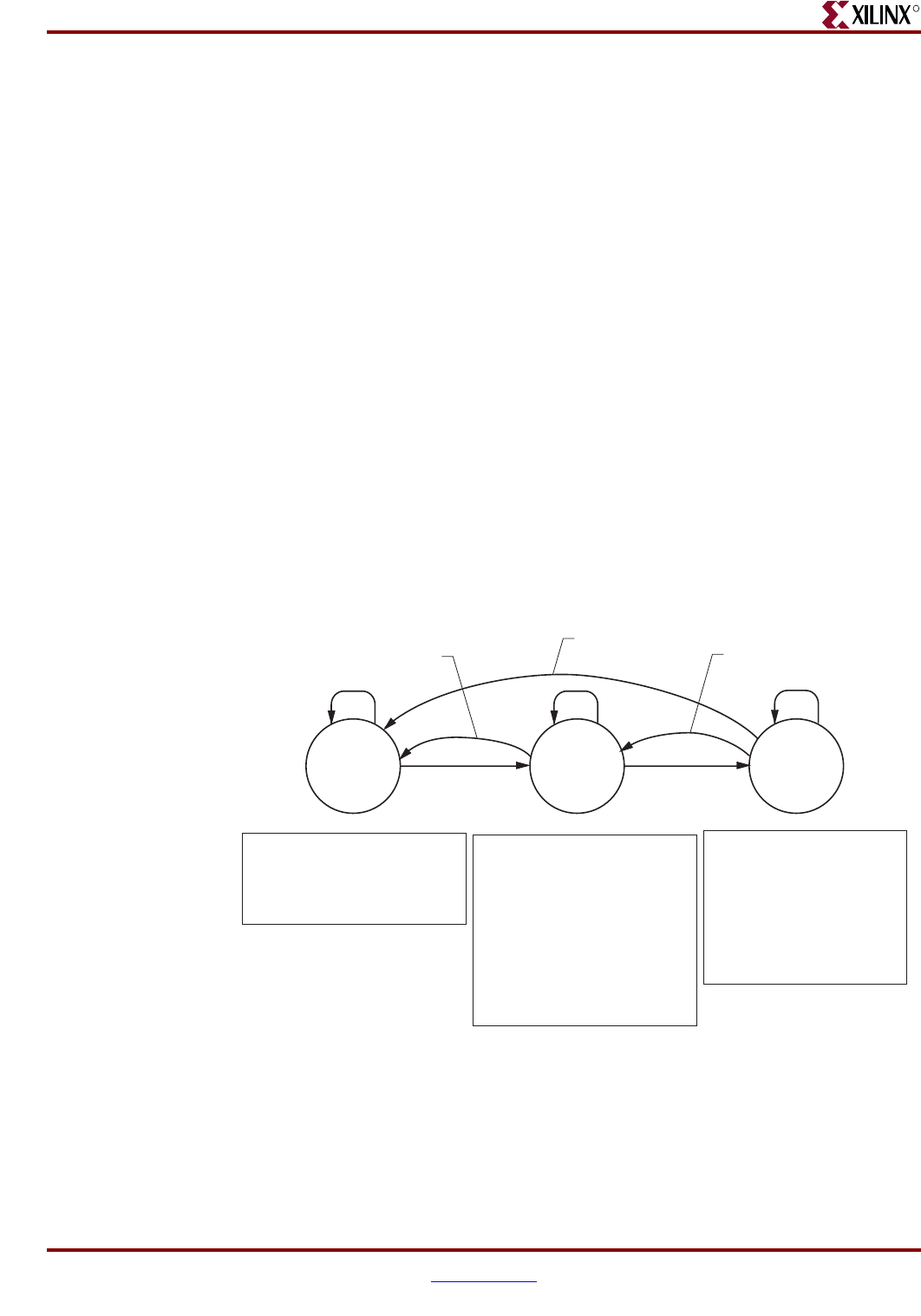

Figure 4-37: Source Startup Sequence State Machine

<NumDip2Errors> Consecutive

Incorrect DIP-2 Calculations Deleted

or Source Disabled

Reset Asserted

Reset Asserted

The Source core remains in the reset state

until the following condition is true:

Reset_n is deasserted

The source core transmits idle patterns

on TDat[15:0] while in the reset state.

The Source core remains in the hunt state

until the following conditions are:

-- The PHY device is no longer sending

framing (TSTAT /= "11")

-- Once framing is not being received, a

consecutive number of DIP2 matches

(defined by the parameter

<NumDip2Matches> is received.

-- Source is enabled

Each "11" to non "11" transition is

translated as a start of a status sequence.

The source core transmits training patterns

on TDat[15:0] while in the hunt state.

In the sync state, the Source core has

completed the start-up sequence and

normal core operation is enabled.

In normal operation, the Source core

transmits data bursts that have been

written into the Source FIFO. It also

sends periodic training patterns on TDat

and continuously checks DIP-2 parity

on TStat.

RESET

HUNT SYNC