SPI-4.2 Lite v4.3 User Guide www.xilinx.com 69

UG181 June 27, 2008

Sink Core

R

FIFO Almost Full Mode “10” or “11”

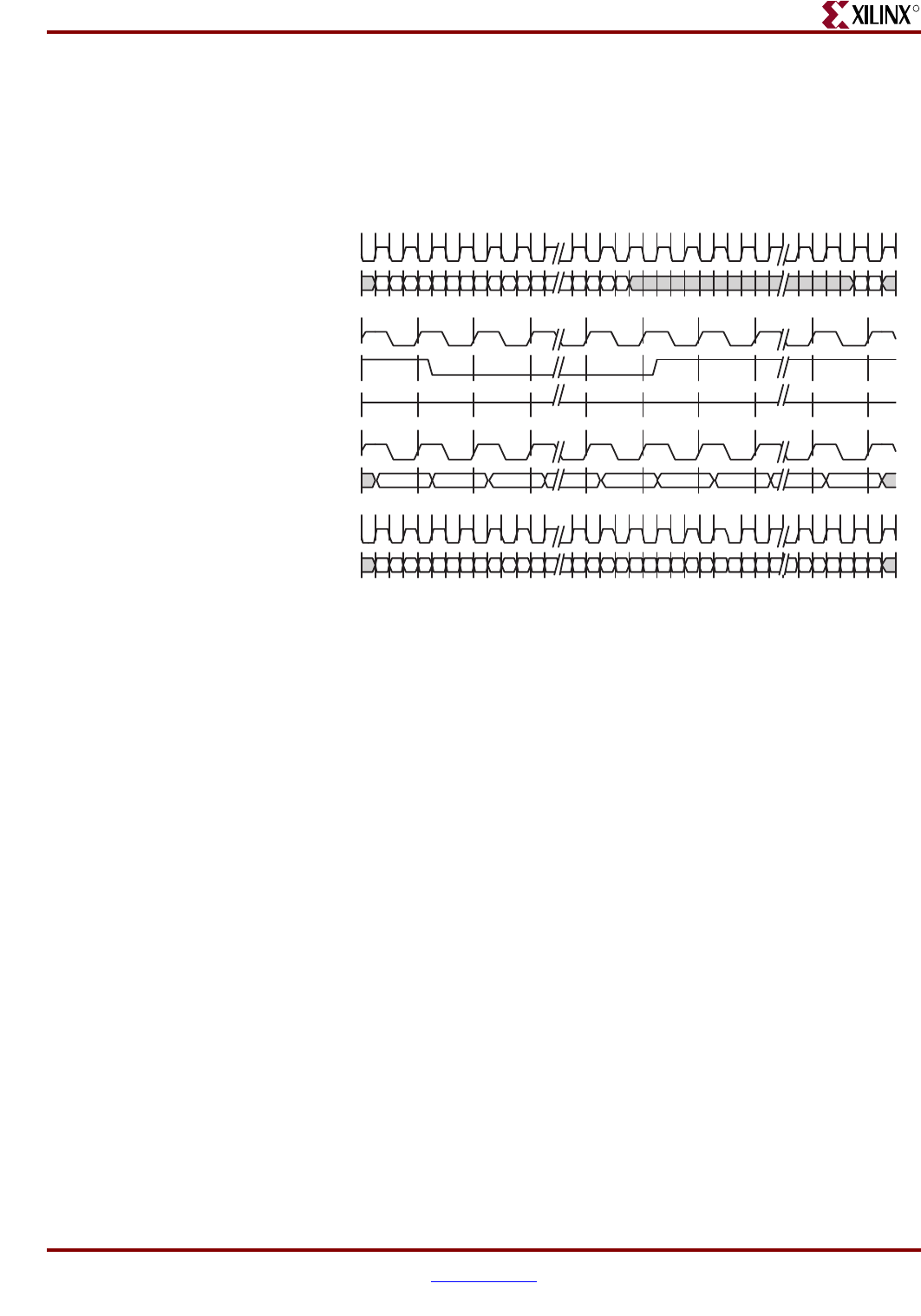

When the FIFO Almost Full Mode (FifoAFMode) is set to “10” or “11,” and the Sink core

becomes Almost Full, the Sink Status logic will continue to drive out user status

information (that is, continue in normal operation). In this last case, take immediate action

to prevent FIFO overflow and loss of data. This is illustrated in Figure 4-14.

Sink Data Capture Implementation

The SPI-4.2 Lite core supports static alignment of the RDClk to RDat[15:0] as defined by

the SPI-4.2 OIF Standard.

Static Alignment

The Sink Core performs static alignment by shifting the clock relative to the 16-bit data

such that the incoming clock edge is centered to the data eye of RDat/RCtl. For designs

using global clocking distribution, this alignment is performed by a DCM. For Virtex-4 and

Virtex-5 FPGA designs using regional clocking distribution, the IDELAY function is used

to shift the clock in relation to the data bits.

DCM Alignment Implementation Considerations

The Sink Core also supports the legacy static alignment, which uses the DCM to phase-

shift the RDClk. The DCM-based static alignment is supported only for global clocking

distribution. The ability of the DCM to shift the internal clock in small increments (~50ps),

enables the RDClk to be shifted relative to the sampled data. For statically-aligned

systems, the DCM output clock phase offset is a critical part of the system. The static

alignment solution, using the DCM, assumes that the PCB is designed with precise delay

and impedance matching for all LVDS differential pairs of the data bus. This assumption is

critical as the DCM does not compensate for deviations in delay between bits.

Determine the optimal DCM setting (PHASE_SHIFT) to ensure that the target system has

the maximum system margin and performance across voltage, temperature, and process

(chip-to-chip) variations. Testing the system to determine the best DCM PHASE_SHIFT

Figure 4-14: FIFO Almost Full Mode “10” or “11”

10 10

DD D D D D DD D D DRDat_P

RDClk_P

D

SnkAlmostFull_n

SnkFFClk

00 00 00 00RStat

RSClk

SnkStat

SnkStatClk

00 00 00 00 10 10 10 10 10 10 10 10 00 00 00 00 00 00

00 10 10 10 10 10 10 10 10 10 10 10 10

SnkOof

D D

00 00 001010 00 00

D D DD D D