SPI-4.2 Lite v4.3 User Guide www.xilinx.com 57

UG181 June 27, 2008

Sink Core

R

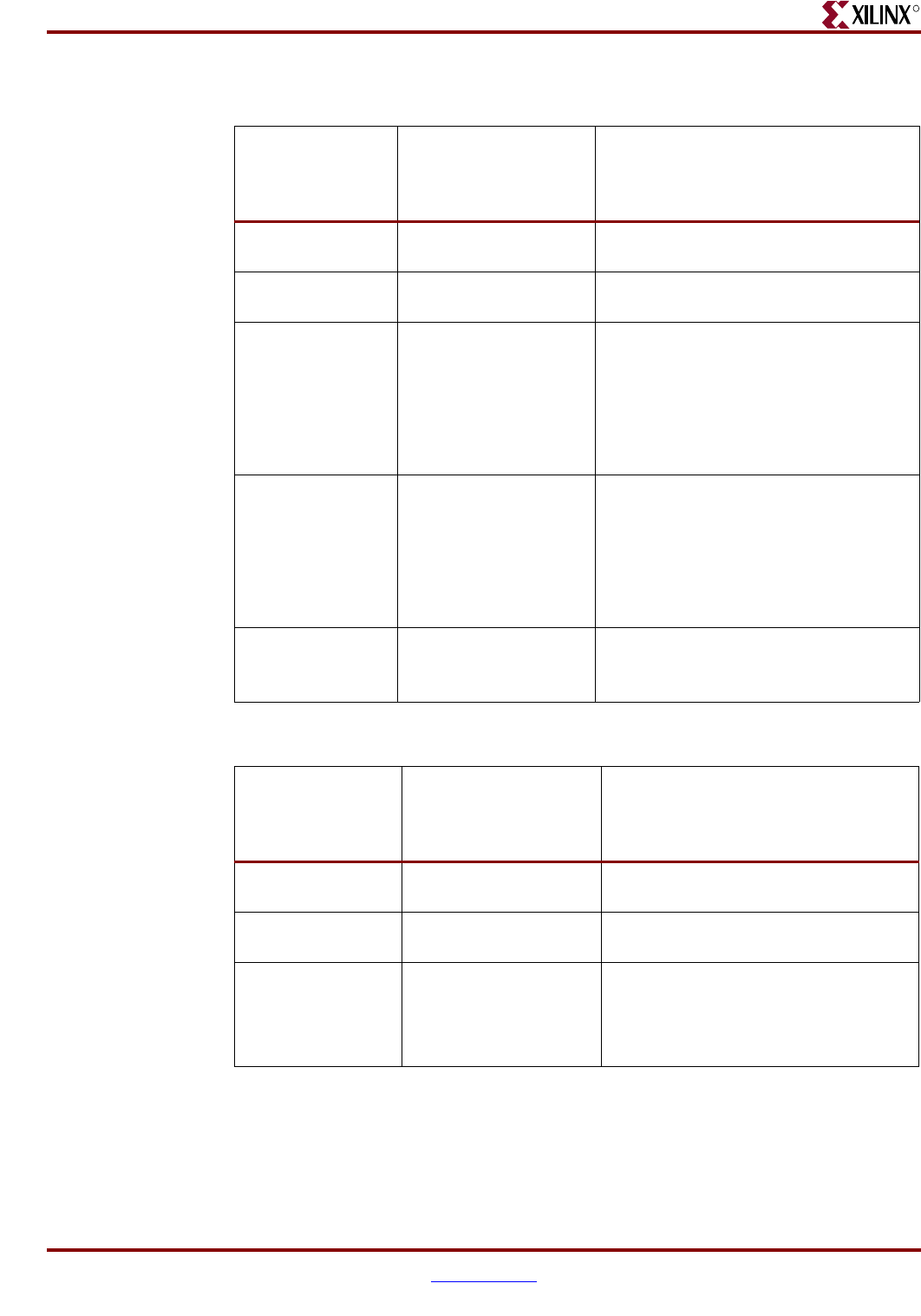

Table 4-2: SPI-4.2 Control Word Mapping to 64-bit User Interface

Control Word

Associated SPI-4.2

Control

Word bits on RDat

(Qualified by RCtl=1)

Associated Sink FIFO Signals

Start of Packet (SOP) RDat[15] = 1, RDat[12] = 1 SnkFFSOP,

SnkFFAddr[7:0] <== RDat[11:4]

New Burst (address

change)

RDat[15] = 1, RDat[12] = 0 SnkFFAddr[7:0] <== RDat[11:4]

End of Packet (EOP,

even bytes valid)

RDat[14:13] = 10 SnkFFEOP, SnkFFMod[2:0]

When RDat[14:13] = 10:

Mod = 000 if data bits 63–0 have valid data

Mod = 110 if data bits 63–16 have valid data

Mod = 100 if data bits 63–32 have valid data

Mod = 010 if data bits 63–48 have valid data

End of Packet (EOP,

odd bytes valid)

RDat[14:13] = 11 SnkFFEOP, SnkFFMod[2:0]

When RDat[14:13] = 11:

Mod = 111 if data bits 63–8 have valid data

Mod = 101 if data bits 63–24 have valid data

Mod = 011 if data bits 63–40 have valid data

Mod = 001 if data bits 63–56 have valid data

End of Packet

(EOP Abort, error

condition)

RDat[14:13] = 01 SnkFFErr & SnkFFEOP

Table 4-3: SPI-4.2 Control Word Mapping to 32-bit User Interface

Control Word

Associated SPI-4.2

Control

Word bits on RDat

(Qualified by RCtl=1)

Associated Sink FIFO Signals

Start of Packet (SOP) RDat[15] = 1, RDat[12] = 1 SnkFFSOP,

SnkFFAddr[7:0] <== RDat[11:4]

New Burst

(address change)

RDat[15] = 1, RDat[12] = 0 SnkFFAddr[7:0] <== RDat[11:4]

End of Packet

(EOP, even bytes

valid)

RDat[14:13] = 10 SnkFFEOP, SnkFFMod[1:0]

When RDat[14:13] = 10:

MOD = 10 if data bits 31–16 have valid data

MOD = 00 if data bits 31–0 have valid data