18 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 2: Core Architecture

R

data access and facilitates integration within a system. Dedicated signals are used to

configure the Sink and Source cores in circuit and monitor a suite of status registers.

Sink Core

The Sink core receives data from the SPI-4.2 interface. It takes the 16-bit interface and maps

it to a 32-bit or 64-bit interface enabling the internal logic to run at a half (for 32-bit) or an

quarter (for 64-bit) of the line rate. The user data and the corresponding control signals are

accessed with a standard FIFO interface. The FIFO read and write operations are

performed in independent clock domains.

The Sink core implements the following features:

• Supports 32-bit or 64-bit user data width

• Dedicated output signal indicating loss of valid RDClk

• Provides a FIFO reset signal for clearing contents of the data pipe during operation

• Provides support for forcing the insertion of DIP-2 errors for system testing

• Regional clocking option (for Virtex-4 and Virtex-5 devices only, saves global clocking

resources)

• Provides both embedded and user clocking options

For more information on core features, see Chapter 4, “Designing with the Core.”

Source Core

The Source core transmits data on the SPI-4.2 interface. Payload data written into the core

as 32-bit or 64-bit words (two or four 16-bit SPI-4.2 Lite words, respectively) are mapped

onto the 16-bit SPI-4.2 interface. While packet data written into the core may not be 32-bit

or 64-bit aligned, the core optimally maps the data to 16-bit words such that no filler idle

cycles are inserted. The data along with the control signals are written into the core via a

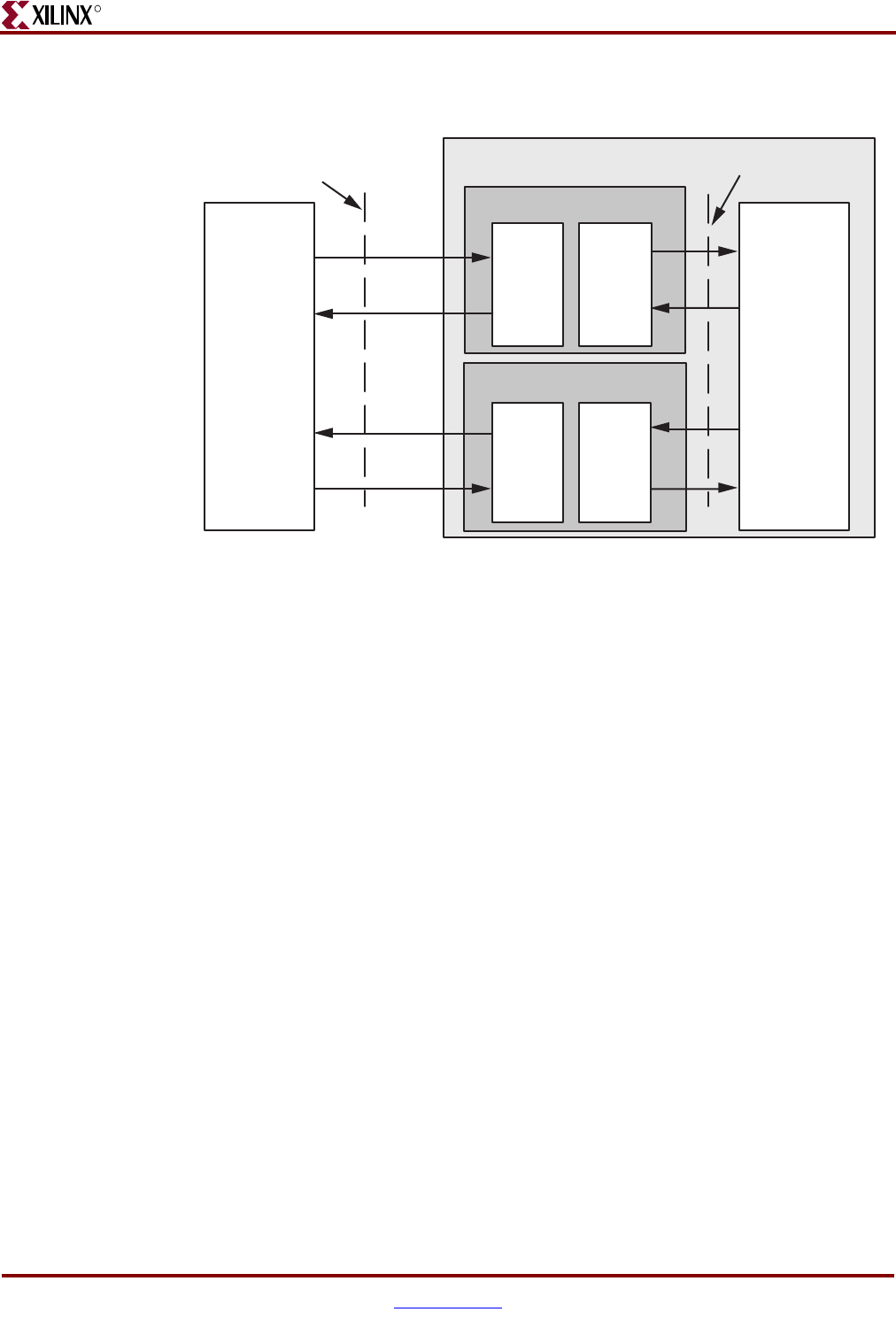

Figure 2-1: SPI-4.2 Lite Core in a Typical Link Layer Application

Virtex-4 or Spartan-3 Device

SPI-4.2 Lite Source Core

SPI-4.2

Interface

User

Interface

SPI-4.2 Lite

PHY Layer Device

(Xilinx FPGA

or

ASSP)

User’s Logic

(Link Layer

Processor)

SPI-4.2 Lite Sink Core

User

Sink

Interface

SPI-4.2

Sink

Interface

Rx Data Path

Rx Status Path

Tx Data Path

Tx Status Path

User

Source

Interface

SPI-4.2

Source

Interface