112 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 6: Special Design Considerations

R

User Clocking

The Sink user clocking configuration allows users to fully customize the way the Sink core

clocks are implemented. An example file is provided (pl4_lite_snk_clk.v/.vhd) that

shows how to implement a clocking module for the Sink core. An illustration of the User

clock inputs and this example module are shown in Figure 6-2 and the user inputs are

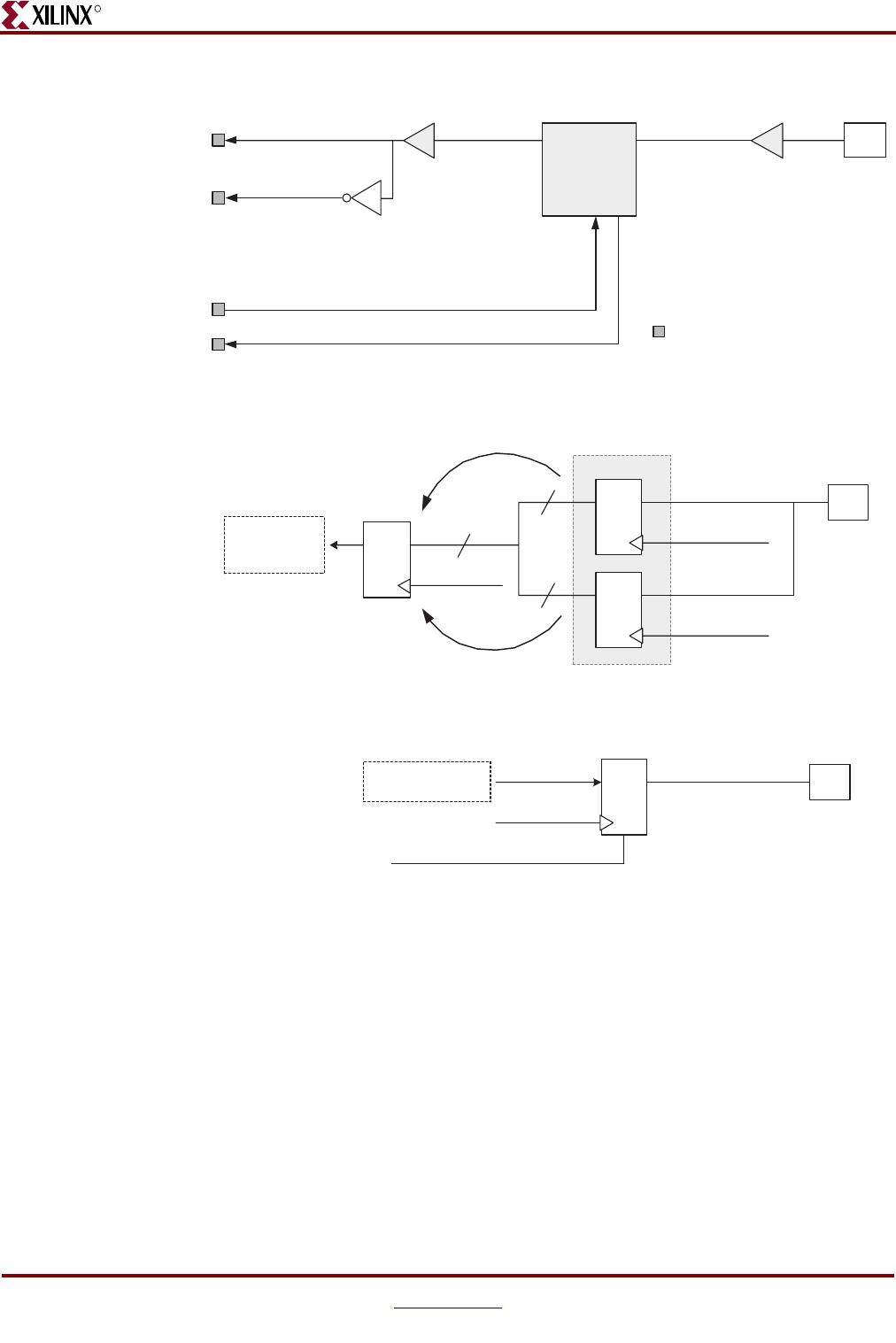

Figure 6-1: Embedded Clocking Option

RDClk0_USER

IOB

RDClk

DCMReset_RDClk

Locked_RDClk

Denotes I/O on User Interface

RDat[15:0] & RCtl

IOB

Q D

Q D

RDClk0_GP

RDClk180_GP

IOB DDR Flops

CLK2X

RDClk0_GP

Q D

Sink Internal

Data & Control

Bus

RDClk0_GP

D Q

EN

Enable at ¼ (or 1/8) PL4 Rx data rate

IOB

RStat[1:0] & RSClkInternal Bus

RStat[1:0] & RSClk

CLK0

CLK180

DCM

100 MHz

100 MHz

100 MHz

100 MHz

100 MHz

100 MHz

25 MHz

32

16

16

200 MHz Path

RDClk180_USER

IBUFGDSBUFG

100 MHz Path