92 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 4: Designing with the Core

R

deasserted (equal to zero), the interface is receiving DIP-2 or framing and the data on

SrcStat[1:0] is not valid. For the Transparent Interface, all outputs use the SPI-4.2

Interface clock domain (TSClk_GP).

Table 4-11 presents status for the 256-channel Source Calendar Initialization system:

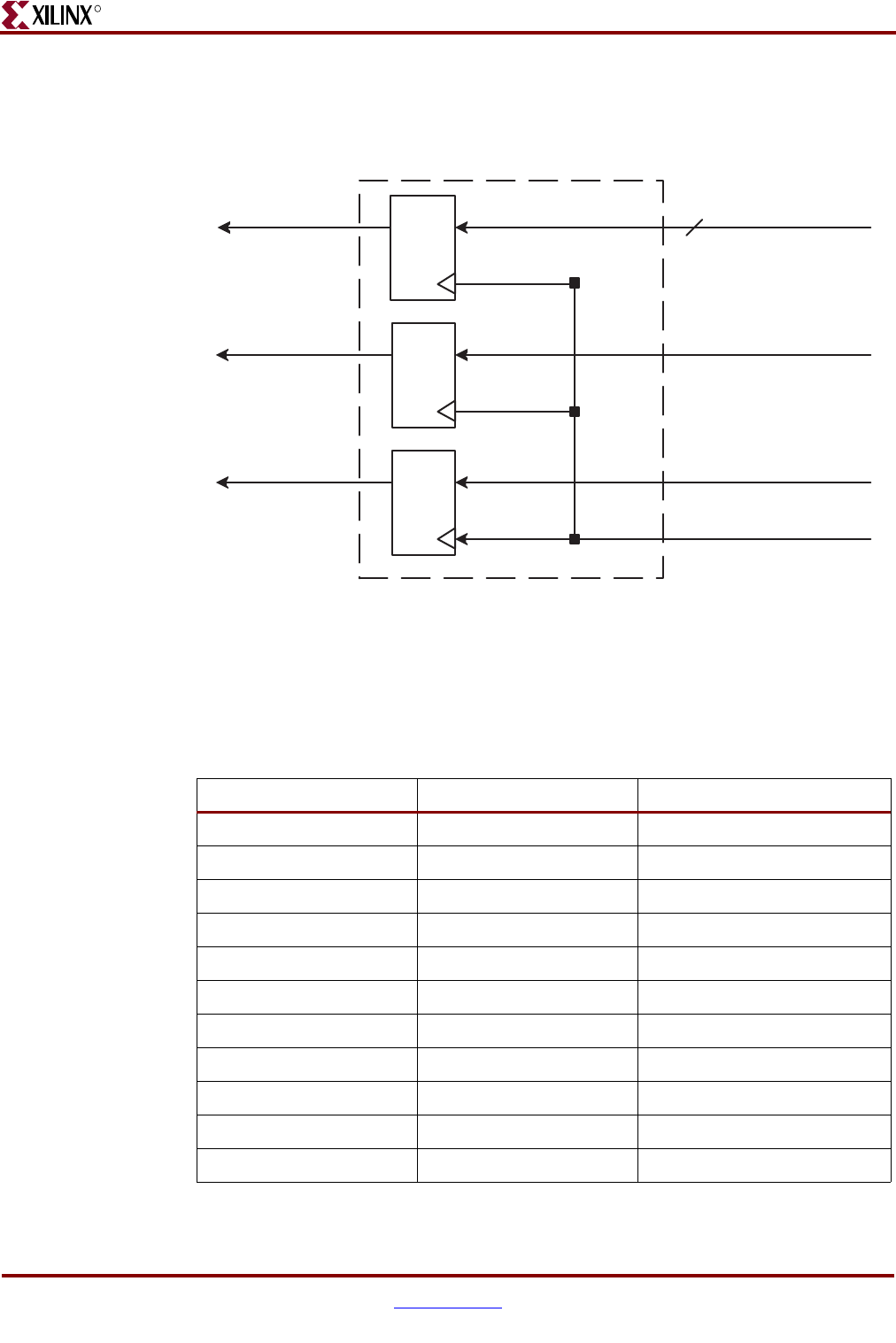

Figure 4-33: Transparent Status FIFO Interface Block Diagram

Table 4-11: Status for the 256-channel Source Calendar Initialization System

Read Cycle Channel Status

00Hungry

12Satisfied

2 128 Starving

3 129 Hungry

49Hungry

51Satisfied

6 Invalid Invalid (DIP-2)

7InvalidInvalid (Frame word)

810Starving

979Hungry

10 16 Satisfied

SrcStat[1:0]

Q D

TSClk_GP

TStat_Delayed[1:0]

TSClk_GP

Write_En

FifoWrAddress

1

SrcStatCh[7:0]

Q D

SrcStatChValid

Q D

TSClk_GP

2

1

FifoWrAddress is the channel address

retrieved from the Calendar.