SPI-4.2 Lite v4.3 User Guide www.xilinx.com 33

UG181 June 27, 2008

Source Core Interfaces

R

Source Control and Status Interface

The Source Control and Status signals either control the operation of the entire Source core

or provide status information that is not associated with a particular channel (port) or

packet. Table 2-11 defines the source control and status signals.

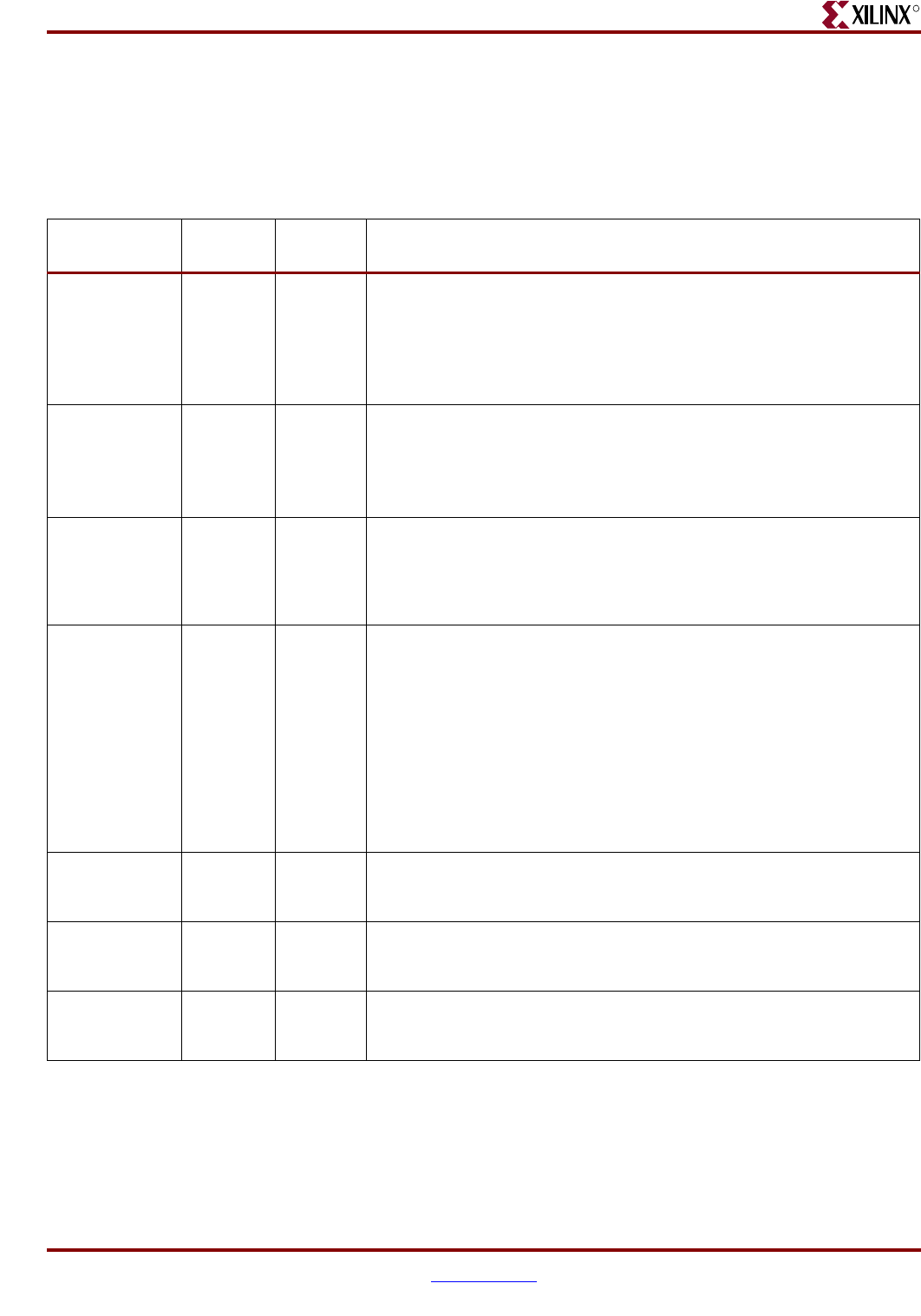

Table 2-11: Source Control and Status Signals

Name Direction

Clock

Domain

Description

Reset_n Input n/a Reset_n: This active low, asynchronous control signal enables you to restart the

entire Source core. This means that the core will go out-of-frame. While Reset_n

is asserted, the Source core transmits idles cycles on TDat. Coming out of

Reset_n, the Source core transmits training patterns.

Following the release of Reset_n, the Source Calendar should be programmed

if the calendar is to be initialized in-circuit.

SrcFifoReset_n Input SrcFFClk SrcFifoReset_n: This active low control signal enables you to reset the Source

FIFO and the associated data path logic. This enables the FIFO to be cleared

while remaining in frame.

Upon Source FIFO Reset, the Source core sends idle cycles until you writes data

into the FIFO.

SrcEn Input SrcStatClk Source Enable: Active high signal that enables the Source core. When SrcEn is

deasserted, the Source core will not store or verify received status information.

The Source core will also assert SrcOof, and deassert SrcDIP2Err and

SrcPatternErr. When SrcEn is deasserted, the Source core will transmit training

patterns on TDat.

SrcOof Output SrcFFClk Source Out-of-Frame: When this signal is asserted (active high), it indicates

that the SPI-4.2 Lite Source core is not in frame. This signal is asserted when the

Source core has lost synchronization on the transmit FIFO status interface. This

is caused by the receipt of consecutive DIP-2 parity errors (determined by the

parameter NumDip2Errors), invalid received status frame sequence (of four

consecutive frame words "11"), or when SrcEn is deasserted.

This signal is deasserted once the Source core reacquires synchronization with

the SPI-4.2 transmit Status Channel. Synchronization occurs when consecutive

valid DIP2 words (determined by the Static Configuration signal

NumDip2Matches) are received and SrcEn is asserted.

SrcOofOverride Input SrcFFClk Source Out-of-Frame Override: When this signal is asserted, the source core

behaves like it is in frame and sends data on TDat, regardless of the status

received on TStat. This signal is used for system testing and debugging.

SrcDIP2Err Output SrcFFClk Source DIP-2 Parity Error: When this signal is asserted (active high), it

indicates that a DIP-2 parity error was detected on TStat. This signal is asserted

for one clock cycle each time a parity error is detected.

SrcStatFrameErr Output SrcFFClk Source Status Frame Error: When this signal is asserted (active high), it

indicates that a non “11” frame word was received after DIP2 on TStat. This

signal is asserted for one clock cycle each time an error frame word is detected.