SPI-4.2 Lite v4.3 User Guide www.xilinx.com 91

UG181 June 27, 2008

Source Core

R

internal status path clock (SrcStatClk) is synchronous to the external status path clock

(TSClk). In other words, SrcStatClk is tied to TSClk_GP. This enables one to always be

accessing the last updated status information, which is achieved by connecting

SrcStatAddr directly to the most significant four bits of the SrcStatCh bus.

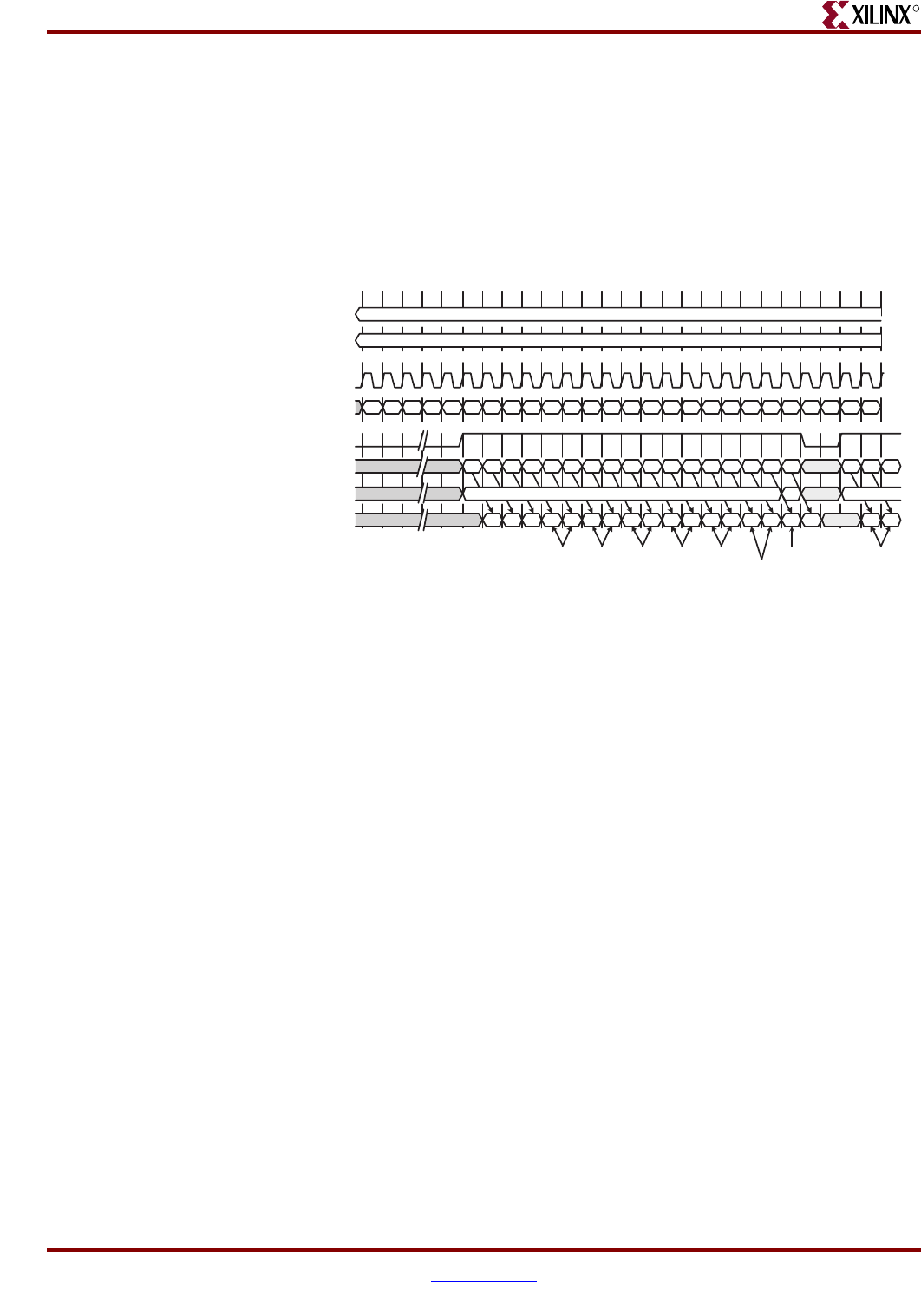

In this example, the status for each channel alternates between starving and satisfied. To

read the status for the full sequence, first set the SrcStatAddr to zero for channels 0-15,

and then to one to address channel 16. Notice that during the DIP-2 and framing cycles, the

SrcStatValid is deasserted. During this time, the output on the bus is not defined.

FIFO status information is periodic, repeating the sequence of a frame word (11), a

repeated set of FIFO status words (SrcCalendar_M + 1 times) in accordance with the

programmed calendar order, and a DIP-2 value. Figure 4-32 shows the receipt of one

complete calendar sequence followed by the beginning of a second sequence. At startup,

the circuitry initializes the Calendar buffer as described (See “Source Calendar

Initialization,” page 86) and asserts the Source Enable signal (SrcEn). After reset is

deasserted, the Source Interface sends training patterns on the data path (TDat[15:0]),

and looks for non-framing data on the status path (TStat[1:0]). When

NumDip2Matches valid DIP2 values are received on the status path, valid data can be sent

on the SPI-4.2 data path. If there is no data in the Source FIFO to be sent, the core sends idle

cycles.

Source Flow Control: Transparent Status Interface

The Transparent Status Interface is 2 bits for all channel configurations. For the Transparent

Interface, you are presented with the current status received on the SPI-4.2 Interface. The 2-

bit status is presented to you by a corresponding channel address (SrcStatCh[7:0]

) and is

qualified with the valid signal SrcStatChValid. Unlike the Addressable Interface, the

transparent interface does not store the received status in a cyclic buffer. This means you

can not access the status of a specific channel, but receives the status in real time as it is

received by the Source core. A block diagram of how the Transparent Interface processes

the received SPI-4.2 FIFO Status is shown in Figure 4-33. The minimum latency between

the user interface and SPI-4.2 Interface for this Status Path interface is 4 TSClk_GP cycles.

Figure 4-34 illustrates the output of the Transparent Status FIFO Interface for a 256-channel

configuration. On each clock cycle, the status (SrcStat[1:0]) and its corresponding

channel (SrcStatCh[7:0]) is presented. The Source Status and channel address are only

valid when SrcStatChValid is asserted (equal to one). When SrcStatChValid is

Figure 4-32: Addressable Status FIFO Interface - SPI-4.2 Interface to User Interface

0 = 0000 0000

16 = 0 0001 0000

SrcCalendar_M

SrcCalendar_Len

TSClk = SrcStatClk

TStat

11 00 10 00 10 00 10 00 10 00 10 00 10 00 10 00 10 dip 1100 10 00 10 00 10 00

SrcStatValid

0x888 0x8888 0x88888 0x888888

0x8888888

0x88 0x8888888A0x88888888

SrcStatCh[7:0]

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 0 1 2

SrcStat[31:0]

SrcStatAddr[3:0] =

SrcStatCh[7:4]

HEX

0x8 0x8 0x00x0

0

1

0