118 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 6: Special Design Considerations

R

Regional Clocking

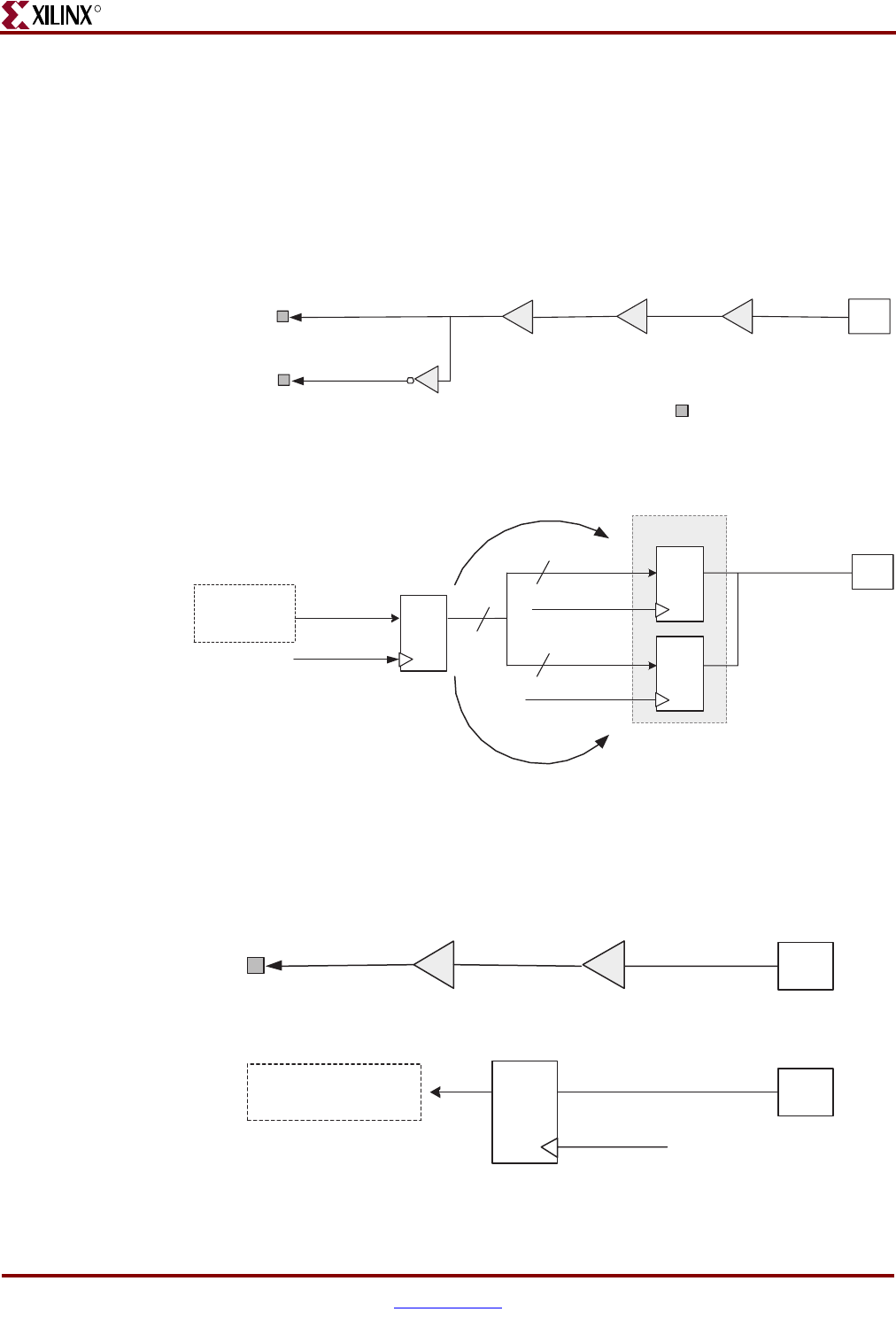

For Virtex-4 and Virtex-5 device designs, this implementation uses the regional clock

buffer resources BUFIO and BUFR to generate a full-rate clock (SysClk0_GP), an inverted

full-rate clock (SysClk180_GP) and the quarter-rate clock (TSClk_GP). The regional

clocking implementation for SysClk is illustrated in Figure 6-8 and the regional clocking

implementation for TSClk is illustrated Figure 6-9. Note that the inverter used to generate

the SysClk180 clock will be absorbed into the DDR flops.

Figure 6-8: Source Clocking: Regional Clocking for SysClk

Figure 6-9: Source Clocking: Regional Clocking for TSClk

IOB DDR Flops

D Q

D Q

Denotes I/O on User Interface

TDat[15:0] & TCtl

IOB

SysClk0_GP

SysClk180_GP

Source Internal

Data & Control

Bus

D Q

SysClk0_GP

IOB

SysClk

100 MHz

32

16

16

100 MHz

100 MHz

SysClk0_GP

100 MHz

100 MHz

100 MHz Path

200 MHz Path

SysClk180_GP

IBUFDSBUFIOBUFR

TSClk_GP

IOB

EN

IOB

TStat[1:0]Internal Bus

TStat[1:0]

Q D

TSClk_GP

25 MHz

TSClk

BUFR

25 MHz

BUFIO