94 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 4: Designing with the Core

R

Source Burst Mode Example

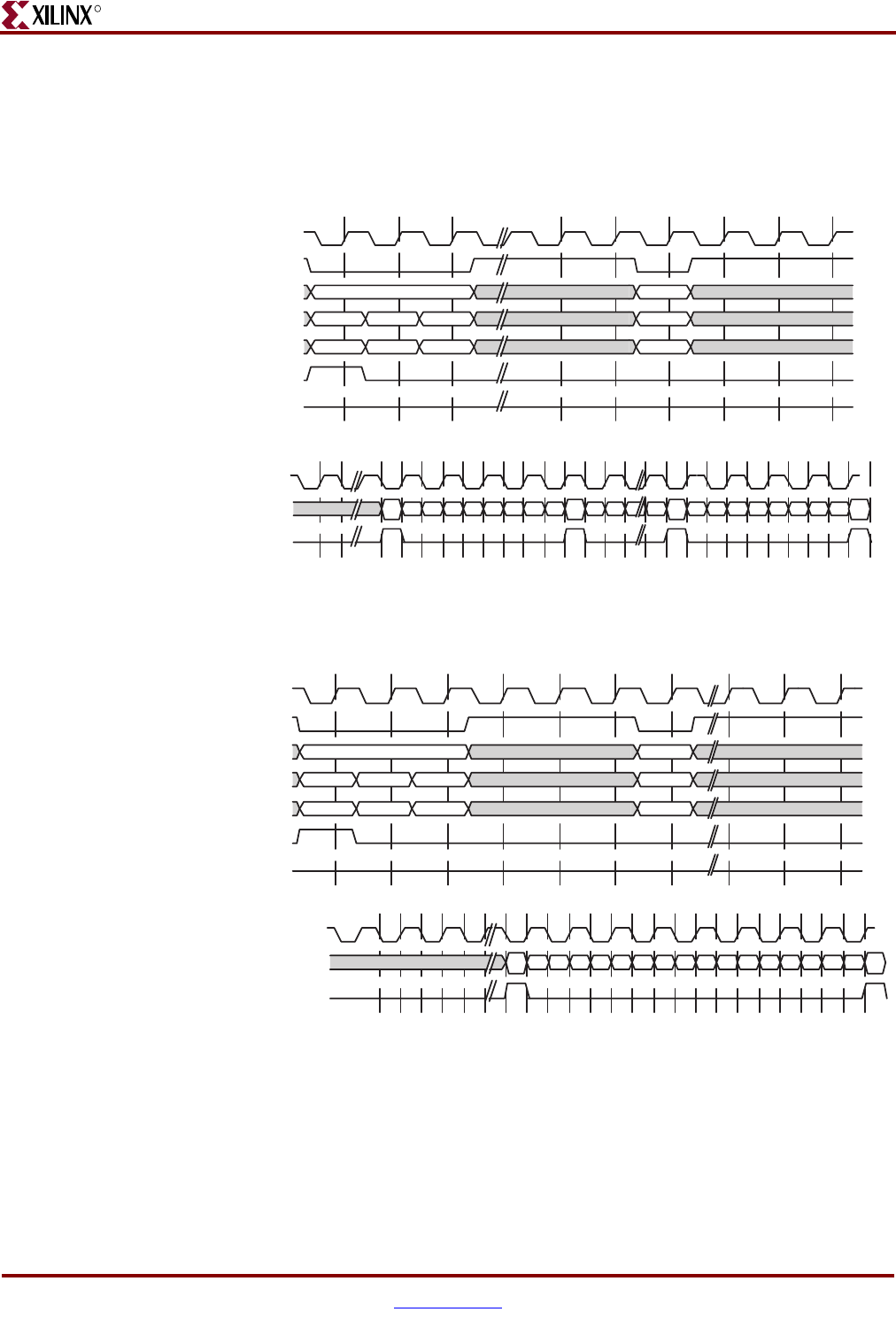

SrcBurstLen equals 2 credits and 1.5 credits are written into the FIFO followed by 0.5

credits. Figure 4-35 illustrates the behavior of the Source core when SrcBurstMode=0.

Figure 4-36 illustrates the behavior of the Source core when SrcBurstMode=1.

Synchronization and Start-up

After the Source core has been initialized, as described in “Initializing the SPI-4.2 Lite

Core,” page 52, the source core has to be synchronized before data and status can be

received and transmitted. Figure 4-37 is a state machine diagram illustrating the Source

core startup and error condition processing.

Figure 4-35: Example Of Source Burst Mode = 0

Figure 4-36: Example Of Source Burst Mode = 1

CH1

04 05 06 0700 01 02 03 10 11 12 13

000000 000

SrcFFClk

SrcFFWrEn_n

SrcFFAddr

SrcFFData

SrcFFMod

SrcFFSOP

SrcFFEOP

TDat_P

TDClk_P

TCtl_P

C1

IDLE

CH1

14 15 16 17

000

C2

IDLE IDLE IDLE

C3

00 01 02 03 04 05 0706 10 11 12 13 14 15 1716

C4

CH1

04 05 06 0700 01 02 03 10 11 12 13

000000 000

SrcFFClk

SrcFFWrEn_n

SrcFFAddr

SrcFFData

SrcFFMod

SrcFFSOP

SrcFFEOP

TDat_P

TDClk_P

TCtl_P

C1

CH1

14 15 16 17

000

00 01 02 03 04 05 0706 10 11 12 13 14 15 1716

C2