64 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 4: Designing with the Core

R

Status for 16 channels each clock cycle can be written. The SnkStatAddr bus is used to

select which 16 channels are written, and the core supports configurations of 1–256

channels. The 16 channels of FIFO Status that are written are addressed as follows:

• Bank 0: SnkStatAddr[3:0]=0 for channels 15 to 0

• Bank 1: SnkStatAddr[3:0]=1 for channels 31 to 16

• Bank 2: SnkStatAddr[3:0]=2 for channels 47 to 32

• Bank 3: SnkStatAddr[3:0]=3 for channels 63 to 48

• ...

• Bank 14: SnkStatAddr[3:0]=14 for channels 239 to 224

• Bank 15: SnkStatAddr[3:0]=15 for channels 255 to 240

The status that is written is mapped to the 16-bit bus as follows:

• For Bank 0: SnkStatAddr[3:0]=0

• SnkStat[1:0] => Channel 0, where SnkStat[1] is the MSB of the 2-bit status

• SnkStat[3:2] => Channel 1

• SnkStat[5:4] => Channel 2

• ...

• SnkStat[11:10] => Channel 13

• SnkStat[13:12] => Channel 14

• SnkStat[15:14] => Channel 15

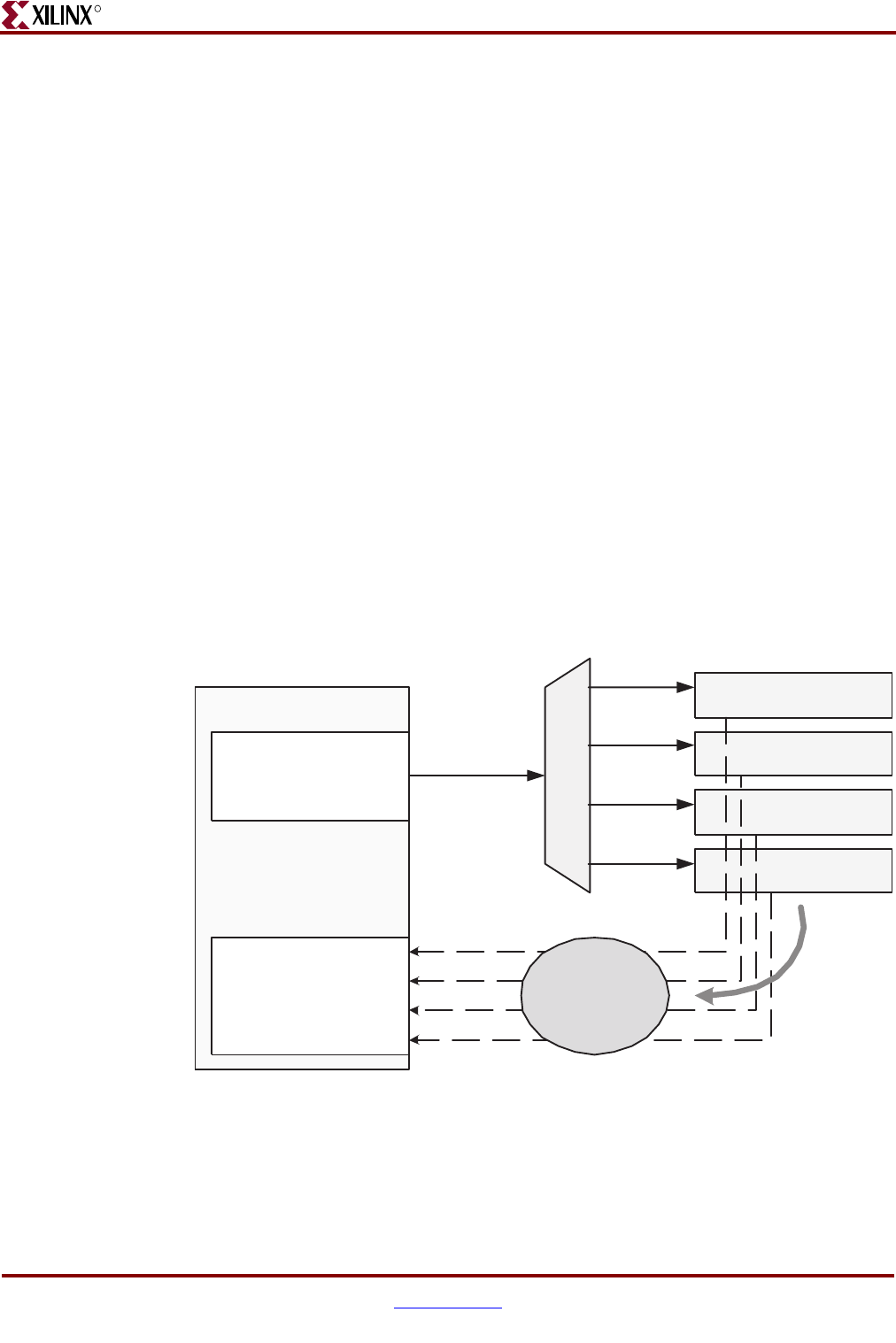

Figure 4-8: Typical Flow Control Implementation for 4-Channel System

FIFO

Channel 0

FIFO

Channel 1

FIFO

Channel 2

FIFO

Channel 3

SPI-4.2 Sink Core

FIFO

Status I/F

User

Interface

MUX

Status:

Starving

Hungry

Satisfied

Flow Control

Programmable

Full